现在看到手机发布会,很多厂商在介绍处理器的时候总会蹦出“FinFET工艺制造”之类的名词,那到底什么是FinFET工艺,到底有什么优势让国际大厂趋之若鹫?

FinFET工艺的概念

FinFET称为鳍式场效应晶体管(Fin Field-Effect Transistor),是由美籍华人科学家胡正明教授提出的,其中的Fin在构造上与鱼鳍非常相似,所以称为“鳍式”,而FET的全名是“场效电晶体” 。

FinFET是一种新的互补式金属氧半导体(CMOS)晶体管,源自于传统标准的晶体管—“场效晶体管”的一项创新设计。

立体式Fin

传统晶体管结构是平面的,所以只能在闸门的一侧控制电路的接通与断开。但是在FinFET架构中,闸门被设计成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种叉状3D架构不仅能改善电路控制和减少漏电流,同时让晶体管的闸长大幅度缩减。

采用FinFET工艺的第三代酷睿处理器

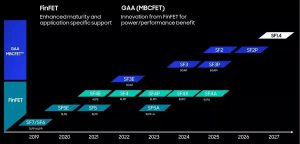

最早使用FinFET工艺的是英特尔,他们在22纳米的第三代酷睿处理器上使用FinFET工艺,随后各大半导体厂商也开始转进到FinFET工艺之中,其中包括了台积电16nm、10nm、三星14nm、10nm以及格罗方德的14nm。

不过FinFET工艺的极限是7nm制程,第一代的7nm工艺还将会继续使用FinFET工艺,但是接下来就需要依赖极紫外光刻机了。

FinFET工艺的制造

前面提到的FinFET可以理解为立体的晶体管,传统平面的晶体管所采用的是FD-SOI工艺。虽然这几年的FinFET工艺占据了大多数人的视线,但是FD-SOI工艺依然非常重要。

如果要是FinFET工艺核FD-SOI达到相同性能,FD-SOI工艺在制造过程中相对简单,但是SOI基片价格稍贵,而FinFET工艺虽然制造过程更为复杂,但是由于基片价格便宜,让两者的实际制造成本相差不大。

前面提到FinFET的制造工艺是非常复杂的,Intel的Mark Bohl在2016年的一个访谈中聊到了FinFET技术,并提到Intel将会继续使用SADP (Self-Aligned Double Patterning)工艺。

其中的Double Patterning是目前主流的FinFET制造工艺。它的原理就是先pattern一批80nm精度的图样,然后再交错Pattern一批80nm精度的图样;在两次光刻之后,就可以将精度提升到40nm。

英特尔的做法就是先用普通精度的光刻可出一堆“架子”,然后在架子上沉淀一层很薄的硅,再选择性的使用把多余的材料弄走,剩下立着的就是超薄的Fin了。准确点来说,这个Fin不是刻出来的,而是长出来的。

FinFET工艺的改良

FinFET工艺实质上就是再原油的基础上增加了一个栅极,这样可以让尺寸很小的晶体管减少漏电。因为大部分的漏电是来自于沟道下方的流通区域,也就是短沟道效应。

那要如何解决掉短沟道效应呢?

就有人开始想:既然电子是在沟道中运动,物理模型需要这片区域来平衡电荷,所以就有了沟道下方的耗尽层。但在短沟道器件里面,把耗尽层和沟道放在一起,等着漏电流白白地流过去。

FD-SOI工艺

于是IBM研究人员开了一个脑洞:把这部分硅换成绝缘层,这样沟道就和耗尽层分开了。因为电子来源于两极,但是两极和耗尽层之间被绝缘层隔开,这样除了沟道外,其他地方就不会产生漏电了,这就是SOI工艺。

SOI工艺虽然没能成为主流,但是依然有很多制造厂在搞,格罗方德和意法半导体就有FD-SOI工艺产品。

英特尔可不这么想:既然要在将耗尽层的硅换成绝缘的氧化物,拿为什么还要放一层没用的硅在下面,直接在氧化层底下弄一个栅极,两边夹着沟道,不是更爽?

现在英特尔还“贪心不足”,于是又想了一个改进方法:那就是把硅弄出来,周围像三明治一样包裹上绝缘层,外面再放上栅极,就有了FinFET工艺。

FinFET工艺的未来

技术节点是衡量半导体技术的重要标准,但并不是绝对的。台积电也好、三星半导体也罢,最挣钱的并不是最先进的技术工艺,而是相对成熟的技术节点。

对于IC设计厂商来说,成本、性能、需求多方面达到平衡的方案和技术节点是最重要的,企业不是慈善家,它也需要考虑盈利的问题,很多芯片在产品性能足够的情况下,选择最合适的制造工艺,可以提升市场竞争力,扩大市场占有率。

台积电在去年的IEDM上发布7nm技术节点的晶体管样品,虽然说台积电的7nm工艺在技术节点与英特尔的10nm非常相似,但台积电已经大有赶超英特尔之势。

7nm制程的FinFET工艺最快要到明年才能面世,7nm也是FinFET工艺的极限,再往下的节点只能看EUV光刻机。

稿源:天极网