近日,在美国举办的Flash Memory Summit(闪存技术峰会)的首日Keynote上,长江存储(Yangtze Memory Technology,YMTC)压轴出场,推出了其最新的3D NAND架构Xtacking,I/O接口的速度提升到了3Gbps,吸引了外界的极大关注。不过在长江存储演讲之前,海力士则公布了更为令人惊叹的4D闪存技术。

长江存储推出3D NAND架构Xtacking

长江存储称,数据产生的能力和贮存能力的增长是严重不对等的,2020年左右将产生47ZB(泽字节,470万亿亿比特),2025会是162ZB。虽然多数数据可能是垃圾,但存储公司没有选择性,其唯一目标就是尽可能多地保存下来。

长江存储将NAND闪存的三大挑战划归为I/O接口速度、容量密度和上市时机,此次的Xtacking首要是提高I/O接口速度,且顺带保证了3D NAND多层堆叠可达到更高容量以及减少上市周期。

当前,NAND闪存主要沿用两种I/O接口标准,分别是Intel/索尼/SK海力士/群联/西数/美光主推的ONFi,去年12月发布的最新ONFi 4.1规范中,I/O接口速度最大1200MT/s(1.2Gbps)。

第二种标准是三星/东芝主推的Toggle DDR,I/O速度最高1.4Gbps。不过,大多数NAND供应商仅能供应1.0 Gbps或更低的I/O速度。

此次,Xtacking将I/O接口的速度提升到了3Gbps,实现与DRAM DDR4的I/O速度相当。

那么长江存储是如何实现的呢?

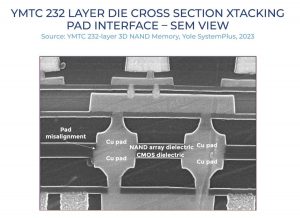

据长江存储CEO杨士宁博士介绍,Xtacking,可在一片晶圆上独立加工负责数据I/O及记忆单元操作的外围电路。存储单元同样也将在另一片晶圆上被独立加工。当两片晶圆各自完工后,Xtacking技术只需一个处理步骤就可通过数百万根金属VIA(Vertical Interconnect Accesses,垂直互联通道)将二者键合接通电路,而且只增加了有限的成本。

官方称,传统3D NAND架构中,外围电路约占芯片面积的20~30%,降低了芯片的存储密度。随着3D NAND技术堆叠到128层甚至更高,外围电路可能会占到芯片整体面积的50%以上。Xtacking技术将外围电路置于存储单元之上,从而实现比传统3D NAND更高的存储密度(长江的64层密度仅比竞品96层低10~20%)。

在NAND获取到更高的I/O接口速度及更多的操作功能的同时,产品开发时间可缩短三个月,生产周期可缩短20%,从而大幅缩短3D NAND产品的上市时间。

长江存储称,已成功将Xtacking技术应用于其第二代3D NAND产品的开发。该产品预计于2019年进入量产,现场给出的最高工艺节点是14nm。

SK海力士推出全球首款4D NAND Flash

在此次的Flash Memory Summit活动上,SK海力士也介绍其在3D NAND的技术路线选择,同时还推出了全球首款4D NAND Flash。目前海力士在NAND市场的全球份额排名第五,DRAM份额全球第二。

首先,在3D NAND的技术路线选择上,SK海力士称,CTF(Charge Trap Flash,电荷捕获型)比Floating Gate(浮栅型)存储单元面积更小、速度更快、更耐用(P/E次数多)。

其实三星从2013年的第一代V-NAND 3D闪存就开始使用CTF了,东芝/西数(闪迪)的BiCS亦是如此。当然,美光/Intel还是坚持浮栅,不过这倒无所谓,毕竟他们有更厉害的3D Xpoint(基于相变内存,还一说是ReRAM磁阻式内存)。

接下来,SK海力士宣布推出了全球首款4D NAND Flash。

从现场给出的技术演示来看,4D闪存和此前长江存储的Xtacking十分相似,只不过外围电路(PUC,Peri.Circuits)在存储单元下方,好处有三点,一是芯片面积更小、二是处理工时缩短、三是成本降低。

参数方面,号称业内第一款4D闪存是V5 512Gb TLC,采用96层堆叠、I/O接口速度1.2Gbps(ONFi 4.1标准)、面积13平方毫米,今年第四季度出样。

BGA封装的可以做到1Tb(128GB),模组最大2TB,塞到2.5寸的U.2中更是可以做到64TB,2019年上半年出样。

性能方面,V5 4D芯片面积相较于V4 3D减小20%、读速提升30%、写速提升25%。

另外,V5 4D也规划了QLC闪存,通过96层堆叠,单Die最小1Tb,明年下半年出样。

从SK海力士公布内部资料显示,其4D闪存已经推进到了128层堆叠,很快可以做到单芯片512GB,2025年做到单芯片8TB。目前,SK海力士的3D NAND是72层堆叠,单芯片最大512Gb(64GB),首款企业级产品PE4010已于今年6月份出货给微软Azure服务器。

综合自:快科技