今天(10月9日)凌晨,在美国加利福尼亚州圣何塞举行的Arm TechCon 2019会议上,Arm首次宣布将在部分ARMv8 Cortex-M系列CPU内核当中引入自定义指令功能,即客户能够编写自己的定制指令来加速其特定用例、嵌入式和物联网应用程序。

引入自定义指令功能

众所周知,目前Arm阵营的芯片设计厂商仅有少数芯片设计厂商有购买ARMv8指令集授权来自行设计CPU内核,比如苹果的A系列处理器的CPU、华为的鲲鹏系列处理器的CPU等。但是,绝大多数的芯片设计厂商都是采用的Arm已经设计完成的内核IP,即外界常说的公版内核,各项性能指标都是已经完全定型了的。

那么在已经定型了的CPU内核的基础上做加速,只能是依靠提升制程工艺来进一步允许主频的提升,或者是依靠处理器当中的其他内核,比如GPU、DSP、NPU等,但他们都是依靠总线来与CPU并行连接和交换数据的。

以CPU和GPU为例,它们之间通过系统总线交换数据的步骤如下:

“第一步:CPU从文件系统里读出原始数据,分离出图形数据,然后放在系统内存中,这个时候GPU在发呆。第二步:CPU准备把图形数据交给GPU,这时系统总线上开始忙了,数据将从系统内存拷贝到GPU的显存里。第三步:CPU要求GPU开始数据处理,现在换CPU发呆了,而GPU开始忙碌工作。当然CPU还是会定期询问一下GPU忙得怎么样了。第四步:GPU开始用自己的工作间(GPU核心电路)处理数据,处理后的数据还是放在显存里面,CPU还在继续发呆。第五步:图形数据处理完成后,GPU告诉CPU,我忙完了,准备输出或者已经输出。于是CPU开始接手,读出下一段数据,并告诉GPU可以歇会了,然后返回第一步。”来源:CSDN

可以看到,其他内核通过内存映射与CPU进行数据交换,都会遇到一个问题,那就是处理器的加速始终是受到总线速度的影响,并且会出现一定的延迟。

当然,芯片设计厂商也可以选择直接连接到CPU的协处理器的解决方案,但是毕竟是两个独立的模块,数据交换也存在着延迟。

而Arm在CPU内核当中引入自定义指令功能,则意味着,芯片设计厂商可以创建自己的加速算法,然后直接在CPU上运行,不需要像内存映射解决方案那样,需要通过总线来并行运行,所以可以在一定程度上进行加速,并进一步降低延迟。

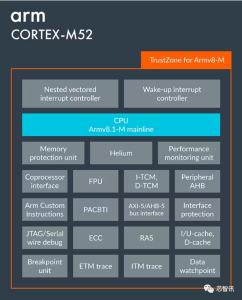

Arm表示,Arm自定义指令是采用安全的Arm TrustZone技术的Armv8-M架构演变的一部分,将成为Arm芯片合作伙伴创新的基础。通过将他们独特的用于特定应用的加速算法添加到Cortex-M33等CPU中,将使得芯片设计人员有机会进一步提高性能和效率。

“自定义指令功能是一种可以增加加速度的方法,虽然还没有深入到CPU更核心的部分,但是为‘我们的客户’提供了更高的灵活性,客户可以编写自己的指令,定义自己的指令,并由CPU来执行这些指令。”ARM汽车和物联网业务高级总监Thomas Ensergueix说到。

此外,Thomas Ensergueix还指出,随着连接设备越来越多,更多Arm的客户将希望针对其非常特定的用例优化其处理器,通过创建自定义指令将可帮助他们更容易的实现性能和效率的提升,同时使得这些设备获得更长的续航。

Arm还表示,自定义指令的加入,为处理器保留了编码空间,以便设计人员可以轻松添加自定义数据路径扩展,可以针对特定应用领域的计算做出优化。同时还可保持现有软件生态系统的完整性。此功能与现有的协处理器接口一起使Cortex-M33 CPU可以使用针对机器学习(ML)和人工智能(AI)等边缘计算用例进行了优化的各种类型的加速器进行扩展。

正如Arm所言,自定义指令的加入,为集成客户工作负载加速提供了最低成本和低风险的途径,因为现有CPU功能没有大的改变,并且仍允许其客户使用他们已经使用的现有标准工具。

Arm首席执行官Simon Segars也表示:“添加此功能后,我们也对如何支持工具流程进行了很多思考。”“这将使所有人都能更快地行动起来。”

而为了推动客户采用新的设计,Arm表示,从2020年开始,使用Cortex-M33内核及之后的Cortex-M CPU内核系列的所有客户都可以免费使用自定义指令功能。

客户纷纷表态认可

目前,Arm已经与多家合作伙伴开始了基于支持自定义指令的处理器的研发,其中就包括IAR Systems,NXP,Silicon Labs和STMicroelectronics。

IAR Systems总裁兼首席执行官Stefan Skarin表示:“ SoC供应商通常需要优化的工具来扩展其设计功能,而又不影响安全性,安全性或现有的开发工具投资(例如IAR Embedded Workbench)。” “自定义指令为他们提供了一种简单但功能强大的机制,可满足他们的独特要求,同时保持已存在流程的完整性和效率。”

恩智浦的Geoff Lees,SVP和GM表示:“ Arm的自定义指令功能使像恩智浦这样的芯片供应商能够为客户提供针对特定应用的指令优化,以提高性能,降低功耗和静态代码大小,以适应新兴的嵌入式应用。”“此外,所有这些改进都在广泛的Cortex-M生态系统中实现,因此客户的现有软件投资得以最大化。”

为什么是Cortex-M系列?

前面我们有提到,自定义指令的优势主要是,芯片设计厂商可创建自己的加速算法,直接在CPU上运行,不需要像内存映射解决方案那样,需要通过总线来并行运行,所以可以在一定程度上进行加速,并进一步降低延迟。

那么为何Arm率先将自定义指令引入到Cortex-M33及后续Cortex-M系列CPU内核当中,而并没有将其引入到Cortex-A系列内核当中呢?

我们都知道Arm Cortex-M系列CPU内核主要应用于对性能要求相对较低、对于功耗和成本要求较高的应用领域,目前在物联网领域应用非常的广泛。而Cortex-A系列内核虽然功耗较高,但是性能也较高,目前手机、平板等对于性能要求较高的处理器,大都是基于Arm Cortex-A系列CPU内核(数据显示,全世界超过95%的智能手机和平板电脑都是基于Arm架构的CPU内核),并且同时还会集成GPU、DSP内核,甚至NPU等专用AI内核。因为,相对于图形及AI计算来说,CPU并不是最佳的载体。而在CPU当中加入自定义指令所带来的性能的提升,相比加入GPU/DSP/NPU等内核所带来的性能提升要小很多,虽然后者的功耗和成本也大幅提升了,但并不像大多数物联网设备那么敏感。

所以,我们不难看出,在CPU当中加入自定义指令功能,对于Cortex-M系列CPU内核所对应的物联网应用领域帮助更大。因为大多数的微控制当中可能只有Cortex-M系列CPU内核。这也意味着,CPU自定义指令功能的加入,可以在无需增加其他的内核,不增加成本和功耗的前提下,帮助客户实现性能的提升(主要是AI性能)。

虽然目前不少的MCU在采用Cortex-M内核的同时,也开始加入了2D的GPU处理单元、DSP内核等,来提升性能,但同时也带来了成本和功耗的大幅提升。而CPU自定义指令的功能的加入,则可以在成本和功耗不变的基础上,进一步提升性能。

如果在CPU当中加入自定义指令的功能,所带来的性能的提升,即可满足客户的需求,那么则意味着客户无需再去集成其他的内核,成本和功耗将进一步得到降低。

当然,如果Cortex-A系列处理器如果也能够引入自定义指令功能,那么也将是一个很好的助力,不过考虑到Arm Cortex-A系列在手机市场的强势地位,以及ARMv8指令集授权的存在,再加上Arm也将推自己的AI IP内核,这一块可能没那么容易。

此举是为应对RISC-V的挑战?

对于Arm来说,受益于其在移动互联网时代所采取的IP授权的模式以及与开放的安卓系统的结合,Arm架构的处理器已经成为了以智能手机为代表的移动互联网设备的标配。经过多年的发展,Arm在移动互联网领域的生态早已是根深蒂固。

但是,随着物联网时代的到来,由于物联网设备品类繁多、应用广泛,市场非常的碎片化,而且很多物联网设备本身即是“操作系统”,即是“应用”,原本在移动互联网设备上极为重要的操作系统、APP,到物联网设备上已变得不再重要。而这也直接导致了物联网处理器芯片的架构出现了百花齐放的局面。Arm固有的强大的生态优势放在物联网市场也不再是不可动摇。

特别是近两年来,RISC-V架构的兴起,在物联网市场对于Arm发起了强有力的挑战。

因为RISC-V架构是一种开源的处理器架构,因此芯片设计厂商可以免费使用RISC-V架构,不需要像使用Arm的处理器IP那样,需要一笔不菲的授权费。而且,传统的Arm处理器IP通常是不允许做扩展的,但是RISC-V则可以方便的进行扩展。这种可扩展可定制化的特点对于场景驱动、性能功耗需求各不相同的AIoT芯片特别重要。显然,对于物联网芯片设计厂商来说,使用RISC-V架构来做AIoT芯片,不仅可以更加的自主可控,还能够更加的灵活,成本也将更低。

由于开源、免费、精简、模块化及可扩展等优点,RISC-V架构受到了全球众多芯片设计厂商的关注,特别是在国内市场,在“自主可控”、“国产替代”趋势之下,RISC-V更是备受追捧。

目前国内的平头哥、兆易创新、华米、乐鑫、芯来、格兰仕等众多厂商都有推出基于RISC-V架构的芯片,此外华为也在积极的研发基于RISC-V架构的芯片。

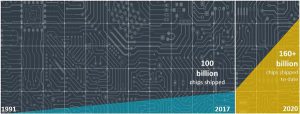

根据市场研究机构IP Nest此前发布的IP市场分析报告显示,2018年全球最大的IP提供商Arm的营收出现了3%的下滑(2017年下滑了6.8%)。IP Nest认为其中一个主要原因应该是来自于开源的RISC-V架构的冲击。

不过,需要指出的是,虽然RISC-V来势汹汹,但是其在高性能这块与Arm的Cortex-A系列内核仍有较大差距,其优势更多还是在于免费、低功耗、易扩展等,这也使得目前RISC-V的应用生态主要集中在物联网领域。对于Arm的威胁也主要是在物联网市场。

对此,Arm也针对性的采取了一些措施。

今年7月,Arm调整了芯片设计授权费的收费模式,推出了全新的Arm Flexible Access业务模式。通过Arm Flexible Access模式,如果芯片制造商使用Arm的一种设计方案投产芯片,那么他们每年需要支付7.5万美元的费用;如果他们每年支付20万美元,那么就可以获得不限数量的芯片设计方案。只有在芯片开始生产时,他们才需要支付授权费和专利费。

不过,需要指出的是,在这个IP包当中,CPU IP只包含了Cortex-A53/A35/A34/A32/A7/A5,Cortex-R52/R8/R5,Cortex-M0/M0 /M3/M4/M7/M23/M33等。

可以看到,高性能的Cortex-A系列处理器并未包含在其中,包括在其中的Cortex-A53/A35/A34/A32/A7/A5均可适用于物联网市场。而主要针对于物联网市场的Cortex-M系列IP基本都囊括在其中。

显然,Arm的“下调IP授权费”之举主要针对的正是物联网市场,主要应对的也正是免费开源的RISC-V架构在物联网市场对于Arm的冲击,提升自身产品在物联网市场的竞争力。

同样,笔者也认为,Arm将自定义指令功能引入Cortex-M33及后续Cortex-M系列CPU内核当中,也正是应对RISC-V架构在物联网市场对于Arm的冲击,弥补自身CPU内核在可扩展性上的劣势,以适应物联网市场对于AIoT的需求。

国外Insight64的分析师Nathan Brookwood也表示,自定义指令似乎是对RISC-V的一种竞争性回应,RISC-V也允许在其架构中使用定制指令。这次Arm在客户的压力下提供了类似的功能。

Moor Insights&Strategy分析师Patrick Moorhead也在一封电子邮件中也表示:RISC-V的可扩展性是非常有吸引力的。现在,Arm已在最需要的领域(如物联网和较低级别的控制器)中添加了这些功能。并且可以在同一工具链中使用,这是一个很大的好处。”

另外值得一提的是,Arm今天还宣布将为Mbed OS建立一种治理模型。Mbed OS是用于运行Arm Cortex-M芯片的嵌入式设备的开源操作系统。Mbed OS一直是开源的,但是Mbed OS合作伙伴治理模型将使Arm的Mbed硅合作伙伴在如何通过每月产品工作组会议等工具开发OS方面拥有更多发言权。诸如Analog Devices,Cypress,Nuvoton,NXP,Renesas,Realtek,Samsung和u-blox之类的合作伙伴已经参加了该小组。

显然,为了争夺物联网市场,Arm正在全方位的提升产品竞争力,同时加速生态布局,以回击RISC-V的挑战。

编辑:芯智讯-浪客剑