在此次论坛上,三星宣布推出了全新的17LPV工艺,即Low Power Value的17nm工艺。

实际上,17LPV工艺就是28nm工艺的演进版,其融合了28nm BEOL后端工序、14nm FEOL前端工序,也就是在28nm节点的基础上,加入了14nm FinFET立体晶体管,只需不高的成本,就能享受后者的能效优势。

三星称,17LPV工艺相比传统28nm,芯片面积可缩小43%,可以带来39%的性能提升或者49%的功耗降低。

三星17nm LPV工艺的量产时间没有说,但三星已经宣布第一个服务对象是ISP图像信号处理器,属于三星自家的CMOS传感器产品线。

此外,三星还打造了14nm LPU工艺,即Low Power Ultimate,但并未透露详情,可能也是28nm BEOL加上14nm FEOL。

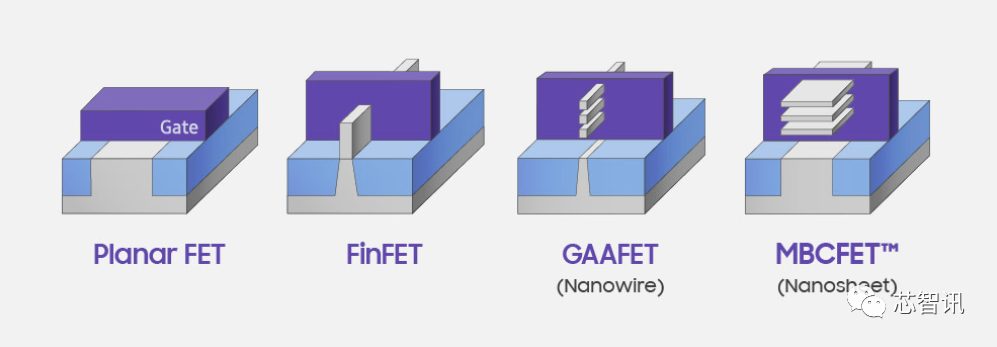

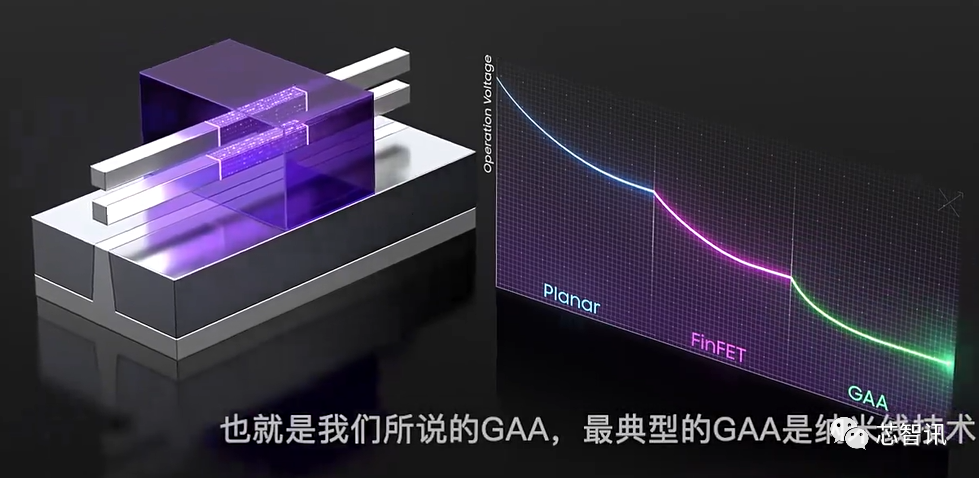

如下图,典型的GAA形式——GAAFET是(Gate-all-around FETs)采用的是纳米线沟道设计,沟道整个外轮廓都被栅极完全包裹,代表栅极对沟道的控制性更好。相比之下,传统的FinFET 沟道仅3 面被栅极包围。GAAFET 架构的晶体管提供比FinFET 更好的静电特性,可满足某些栅极宽度的需求。这主要表现在同等尺寸结构下,GAA 的沟道控制能力强化,尺寸可以进一步微缩。

不过,三星认为采用纳米线沟道设计不仅复杂,且付出的成本可能也大于收益。因此,三星采用了全新的GAA形式——MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),采用多层堆叠的纳米片来替代GAAFET中的纳米线。

三星表示,MBCFET可以在保留所有GAAFET优点的情况下,最小化复杂度。同时,MBCFET的设计可以兼容之前的FinFET技术,可以直接将为FinFET的设计迁移到MBCFET上,在不提升面积的情况下,提升性能。

在此次论坛上,三星强调,与其5nm制程相较,三星首个3nm GAA 制程技术将使得芯片面积可再减少35%,性能可提高30%或功耗降低50%。除了功耗、性能和面积(PPA) 上改进,随着制程技术成熟,3nm良率将会接近4nm制程。三星预计2022 年推出第一代3nm 3GAE 制程技术,2023年推出更新一代的3nm 3GAP 制程技术。

目前在晶圆代工市场,特别是在先进制程的竞赛当中,所需要的研发资金投入以及产线建设成本是越来越高。为此,在该领域目前也只剩下了台积电、三星和英特尔这三家厂商在竞争。

根据此前的资料显示,三星计划在2030年之前投资133万亿韩元(约合1160亿美元),以期成为全球最大的半导体代工企业。台积电也计划在未来三年内投入1000亿美元。英特尔在重启晶圆代工业务之后,也宣布了超过1000亿美元的投资计划,比如在美国投资200亿美元建设两座晶圆厂,未来10年在欧洲投资800亿欧元建设至少两座晶圆厂等。

从资金的投入规模来看,作为目前的全球晶圆代工市场的龙头老大,台积电的在晶圆代工领域的资金投入无疑是最大的。而重启晶圆代工业务的英特尔也是来势汹汹。在此背景之下,三星的晶圆代工业务自然也将是面临着更大的压力。

不过,从前面3nm工艺量产时间节点来看,三星有望在3nm上实现对于台积电的反超,并且继续领先于英特尔。而在之后的2nm制程工艺节点,英特尔有望实现对台积电和三星的反超,重新引领全球半导体制程工艺技术。但是,鉴于英特尔此前曾多次跳票的历史,外界对其在2024年量产2nm超越台积电持怀疑态度。

编辑:芯智讯-浪客剑