为因应日益复杂的RFIC 设计要求,新思科技(Synopsys) 近日宣布针对台积电N6RF 制程推出最新的RF 设计流程,此乃新思科技与安矽斯科技(Ansys) 和是德科技(Keysight) 共同开发的最先进RF CMOS 技术,可大幅提升效能与功耗效率。该流程可协助其共同客户实现5G 晶片的功耗与效能优化,同时加速设计效率,从而加快产品的上市时程。

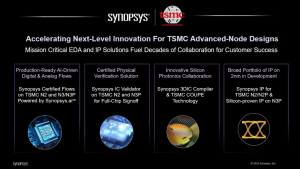

台积电设计建构管理处副总经理Suk Lee 表示,台积电与新思科技近期的合作着重于新一代无线系统的挑战,让设计人员能够为越来越互联的世界提供更好的连接、更高的频宽、更低的延迟(latency) 以及更广的覆盖范围(coverage)。有了来自新思科技、安矽斯科技与是德科技紧密整合的高品质解决方案,台积电全新的针对N6RF 制程的设计参考流程提供了一个现代且开放的方法,能提升复杂IC 开发的生产效率。

由于互联世界的需求,用于收发器 (transceiver) 和 RF 前端元件 (front-end component) 等无线资料传输系统的RFIC 变得日趋複杂。这些新一代无线系统有望在更多连接的装置上提供更高的频宽、更低的延迟以及更广的覆盖范围。为了确保 RFIC 能够满足这些要求,设计人员必须准确地衡量 RF 的效能、频谱 (spectrum)、波长和频宽等参数。

新的RF 设计参考流程采用领先业界的电路模拟、布局生产效率以及精确的电磁(EM) 建模和电子迁移/IR 压降(electromigration/IR-drop EMIR) 分析,可缩短设计周转时间(turnaround time)。该流程包括了新思科技的Custom Compiler 设计和布局产品、PrimeSim 电路模拟产品、StarRC 寄生萃取签核(parasitic extraction signoff) 产品与IC Validator 物理验证产品,以及安矽斯科技的VeloceRF 电感元件(inductive component) 与传输线合成产品、先进的纳米电磁(EM) 分析产品RaptorX 和RaptorH,以及Totem-SC,此外,还有是德科技用于EM 模拟的PathWave RFPro。

新思科技工程副总裁Aveek Sarkar 说,为了实现5G 设计的关键差异化优势,新思科技持续带来强大的RF 设计解决方案,其整合了电磁合成(electromagnetic synthesis)、萃取、设计、布局、签核技术和模拟工作流程。由于新斯科技与台积电的深入合作,加上与安矽斯科技和是德科技的坚实关系,因此客户得以使用新思客制化设计系列的先进功能,运用台积公司针对5G 应用的先进N6RF 技术,提高生产力并实现矽晶成功。