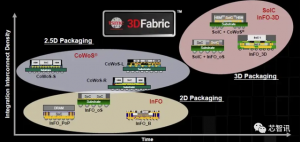

5月16日消息,随著先进制程的发展,芯片尺寸已经接近 1nm的物理极限,摩尔定律正步入尾声,而先进封装技术已成为下一个关键发展方向。尤其是具备高度芯片整合能力的“异质整合”封装技术,已成为超越摩尔定律的重要技术之一。

近期,各国都在扩大先进芯片封装的能力,包括韩系大厂重金挖角对手,以期能在 CoWos(Chip on Wafer on Substrate)和 InFO / InFO-PoP(Integrated Fan-out / Integrated Fan-out-package-on-package)等先进封装技术中弯道超车。

同时,ChatGPT 也带动了高阶人工智能(AI)芯片的封装需求,主要芯片封装与测试企业,也努力通过异质整合的先进封装技术,提升 HPC(高性能计算)性能与储存方面的能力。而台系主要半导体封测大厂,也早已布局 FC-MCM(Flip-Chip-Multi-Chip-Module)、FOCoS(Fan-Out Chip on Substrate)和 VIPack(Vertical Integrated Package)等技术,抢攻 HPC 和 AI 封装市场。

但是,异质整合的先进封装技术,也面临到许多可靠度上的疑难杂症,需要进行前期的验证分析以确认研发品质。

宜特材料分析实验室从“先进封装材料特性”这个面向,来探讨晶体结构、缺陷和应变是如何影响先进封装元件的性能和可靠度。又该如何利用现有工具来掌握这些先进封装材料的特性。并以三大实际案例为您介绍晶体结构的先进分析利器-EBSD。

什么是 EBSD?

我们知道,所有的物质都是由“原子”组成,这些原子可以排列成不同的“晶体结构”,而这些结构决定了物质的特性。

该如何解析晶体结构,就需要靠 EBSD 这项利器。EBSD(Electron Backscatter Diffraction),又称电子背向散射绕射,是一种研究物质微观结构的技术,它可以让研究者像是用放大镜一样,分析材料的晶体结构、晶界和异质材料界面,但更加精确和详细,进而帮助客户优化材料的选择和制程改良。

EBSD 技术的应用范围相当广泛,例如金属、陶瓷、材料科学、工程、电子领域,尤其在半导体制程中,藉以研究晶体结构、缺陷和应变等问题,对进一步提高半导体元件的性能和可靠度有绝对的帮助。

速读:EBSD 原理

电子背向散射绕射(EBSD)是一种在电子显微镜(EM)中使用的非破坏性分析技术。EBSD 是将高能电子束射入样品表面,与样品表面的晶格产生交互作用后,电子会反弹回来,并在萤光屏上形成特定的花纹图样,即所谓的菊池线图。从反射图案中,可获得样品微观结构的资讯。通过资料库比对,即可将样品晶粒的相对位置在空间中进行作图。因此,EBSD 可提供准确的微观晶体结构鑑定。

那么 EBSD 可以怎麽运用?以下是宜特材料分析实验室中实际三大案例分享。

案例一:从铜柱的晶粒尺寸与结构强度推测其抗电迁移能力

铜柱(Copper Pillar)是一种封装技术,广泛应用于半导体芯片和封装基板之间的连接,如 3D IC 封装和 FCBGA(Flip Chip Ball Grid Array)封装。这种技术使用细小的铜柱代替传统的导线,以提高连接的密度和可靠度,并实现更高的 I/O(Input/output)密度和更高的性能。

EBSD 分析技术可以提供铜柱晶体结构的定性分析,包括晶粒尺寸、晶格取向、晶界角度等资讯。这些数据可以用来推测铜柱的抗电迁移能力。

晶粒尺寸:晶粒尺寸越小,晶界密度就越大,因此电子的运动受到的阻碍也就越大,从而抗电迁移的能力就越好。

晶格取向: <111> 晶向的铜柱比 <100> 晶向的铜柱具有更好的抗电迁移能力。这是因为在 <111> 晶向的铜柱中,晶界的面积更小,电子的运动更加容易,因此电子在这种结构中迁移的能力更好。

材料科学小知识

<111> 或(111)是用来表示晶体方向与晶面的一种指数,称为米勒指标(Miller index),是晶体学(Crystallography)中用来确定固体中原子或离子排列方式的一种表示法。

晶界角度:当晶界角度较小时,晶界处的应力更小,晶界也更加稳定。因此,可以预期晶界角度较小的铜柱具有更好的抗电迁移能力。

图一可得知晶界角度大于 10 度的比例为 94%,表示其晶粒取向差异较大,可能较不利于抗电迁移;图二为统计其铜柱晶粒尺寸的结果,其平均粒径为 1.6um,粒径及取向数据需要再进一步比对及分析。不过综合两个结果,意味著铜柱可能不具有较好的抗电迁移能力。宜特材料分析实验室建议,研究者可根据这样的结果,进一步採用高温高湿(HTH)和恆电压(HVM)等分析,测试其抗电迁移能力。

▲图一:铜柱的晶界分布,包含大角度晶界(黑)、小角度晶界(浅灰)与孪晶界(红)。(Source:宜特科技)

▲图二:晶粒尺寸分布统计。(Source:宜特科技)

案例二:从介金属化合物分析,确认铜柱的焊接品质是否良好

在铜柱焊锡接点中,铜和锡在共晶反应后完成焊接,而界面的介金属化合物(Intermetallic Compound,简称 IMC)即是铜锡接合的关键。在良好的焊接过程中,铜锡会形成“表面能”较高的球状结晶(Cu6Sn5)。

然而,随著迴焊温度增加或使用时间增长,接点中的介面会形成劣化的柱状结晶(Cu3Sn),这会降低接点的强度和可靠度。因此,宜特材料分析实验室建议,观察铜锡界面的介金属化合物分布以比较接点强度,进而确认焊接品质是否良好。

如图三所示,铜锡介金属化合物的相分别为桃红色的 Cu6Sn5,以及天蓝色的 Cu3Sn,其相分布状况与比例,可作为评估机械性质的参考。

▲图三:铜柱(含铜锡介金属化合物 IMC)的相分布及其比例。(Source:宜特科技)

案例三:从铜铜接合介面,观察样品机械强度及抗电迁移性

随著制程技术的进步,晶片尺寸的缩小、运算能力的增加,以及连接器接点数量的增多,导致传统使用焊锡作为高密度接点的方式达到极限。微缩焊锡不仅结构强度不足,而且散热性和抗电迁移能力也不足以应付需求。因此,铜-铜接合逐渐成为先进封装的热门技术。

在铜铜接合的方法中,纳米孪晶铜的孪晶界可增加机械强度及降低电迁移的风险,且具有良好的导电性质。因为铜原子在(111)面上的密度最高,该面拥有其他面数千倍的扩散速率。这种方法可以在较低的温度或短时间内快速接合,从而避免高热温度对异质整合的影响,提高良率。而我们藉由 EBSD 分析其晶粒取向(orientation)资讯,就可以提早掌握产品机械强度及发生电迁移的风险。

从图四和图五可以看出,即使是以低温快速接合,但上下两个铜垫片(Cu pad)仍未互相扩散,虽其优选取向为(111),具较佳的抗电迁移能力,但仍然可以明显观察到介面,这意味著机械强度较弱,介面有分离的风险。而图六和图七显示,虽然铜垫片间的介面消失,表示其具较佳的机械强度,但优选取向结果显示其可能不具优异的抗电迁移性质。

▲图四:铜铜接合温度 150 度时的晶界分布,虚线圈选处为铜铜接合介面。(Source:宜特科技)

▲图五:铜铜接合 150 度时的取向分布图(orientation map),虚线圈选处为铜铜接合介面。(Source:宜特科技)

▲图六:铜铜接合 350 度的晶界分布,虚线圈选处为铜铜接合介面。(Source:宜特科技)

▲图七:铜铜接合 350 度时的取向分布图(orientation map),虚线圈选处为铜铜接合介面。(Source:宜特科技)

来源:Technews