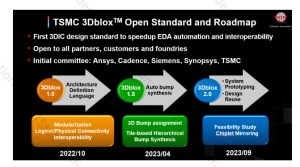

10月13日消息,台积电在欧洲举办2023 台积电开放创新平台(Open Innovation Platform ,OIP)活动,向合作伙伴展示下一代晶圆代工技术,并表示目前芯片设计人员所需的全新的面向2nm制程工艺的EDA、模拟和验证工具及部分IP都已可供使用,相关生态系统正在形成。

台积电计划在2025下半年量产2nm(N2)制程,由于GAA晶体管构架与台积电目前3nm FinFET完全不同,因此配套的EDA工具和IP都需要进行针对性更新。不过,台积电的OIP平台能使合作伙伴提前开始开发产品。

台积电设计基础设施管理事业部处长Dan Kochpatcharin表示,“针对N2,我们可以提前两年合作,因为Nanosheet是不同的。EDA工具必须准备就绪,而OIP能使我们尽早与合作伙伴合作,台积电有庞大的工程团队,可与EDA、IP等合作伙伴合作。”

目前主要的EDA工具厂商Cadence和新思科技,以及Ansys和Siemens EDA等厂商的许多工具都已经通过了台积电认证,不过IP设计则需要更长时间。

根据台积电公布的信息,非易失性內存(non-volatile memory)、接口IP、chiplet相关IP等模块尚未出现,这成为部分芯片设计的瓶颈,但台积电的合作伙伴都正在积极开发。目前用于设计2nm芯片的工具和生态系统正在形成,但还没有全部到位。

Kochpatcharin指出,开发采用Nanosheet晶体管的IP并不难,但确实需要更多、更长的周期时间,部分IP供应商也仍需要接受培训,当接受培训后,设计上就会变得容易,这就是台积电之所以很早就开始的原因。

目前许多芯片的主要建构模块都已支持N2,但在台积电2nm量产前,许多公司仍有许多事情要做。至于设计IP和开发工具的大公司已在开发2nm芯片,到2025年量产时,他们的产品应该已经准备就绪。随着台积电及合作伙伴的2nm准备工作进展顺利,其他芯片设计公司也可以准备设计规划。

编辑:芯智讯-林子