12月19日消息,在上周召开的国际电子器件会议(IEDM 2023)上,台积电发布了一篇标题《面向未来逻辑技术扩展的 48 纳米栅极间距的互补场效应晶体管 (CFET) 》的论文。这篇论文由大约 50 位不同的作者撰写,由 Sandy Liao 发表。

CFET 是一种 CMOS 工艺,其中晶体管垂直堆叠,而不是像所有先前的逻辑工艺那样位于同一平面,比如平面工艺、FinFET、纳米片场效应晶体管(NSFET,也称为环栅或 GAA)。

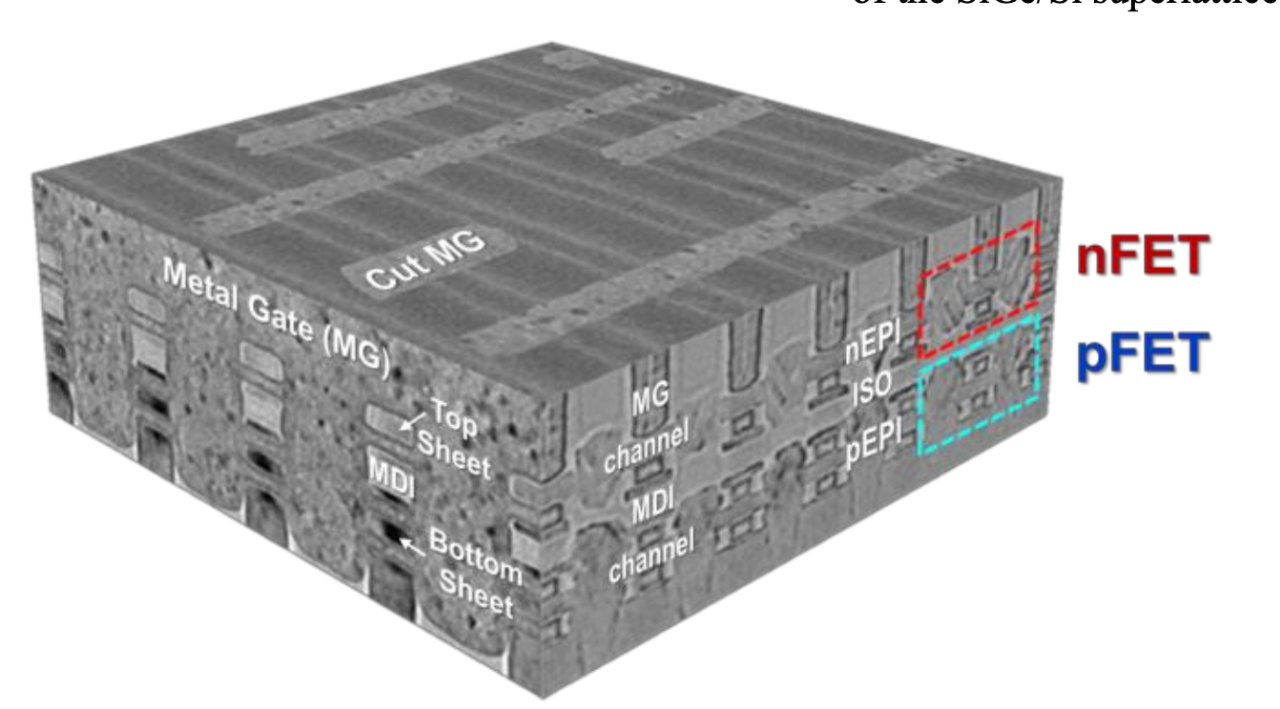

据推测,台积电未来将会采用CFET 工艺,但该论文描述了可制造性的早期研究。该过程将 n 晶体管堆叠在 p 晶体管顶部。在问答中,Sandy被问及做出这一决定的动机是什么。她说,这并不是一成不变的,将来可能会改变,但将 PMOS 放在底部可以更轻松地处理压力。台积电将其称为单片 CFET 或 mCFET。

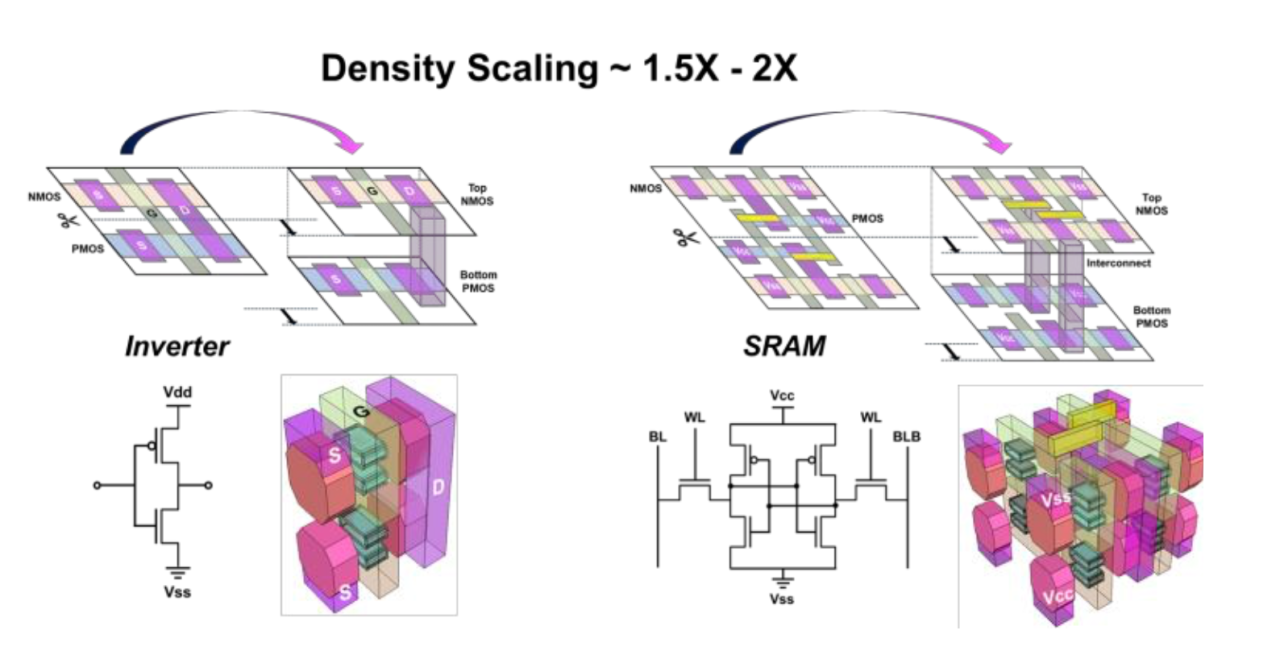

他说,CFET 可以将面积减少 1.5 倍到 2 倍。仍然需要为一些垂直布线留出空间,因此通常无法通过堆叠晶体管获得预期的 2 倍性能。之前对 CFET 制造的研究使用了宽松的栅极间距,但未能成功地将栅极间距控制在 50nm 左右。因此,台积电的这项研究是第一个使用 48nm 栅极间距的研究,Sandy 表示,这“与行业级先进节点缩放相关”。

为了实现这一点,需要使用中间电介质隔离、内部隔离物和 n/p 源极-漏极隔离。该工艺为未来 mCFET 的进步奠定了坚实的基础,这将需要进一步的创新和额外的架构功能。

△这是 mCFET 的 TEM 演示。正如上面所介绍的,nFET 位于顶部,pFET 位于底部。两种类型的晶体管都具有由单个金属栅极包围的沟道。

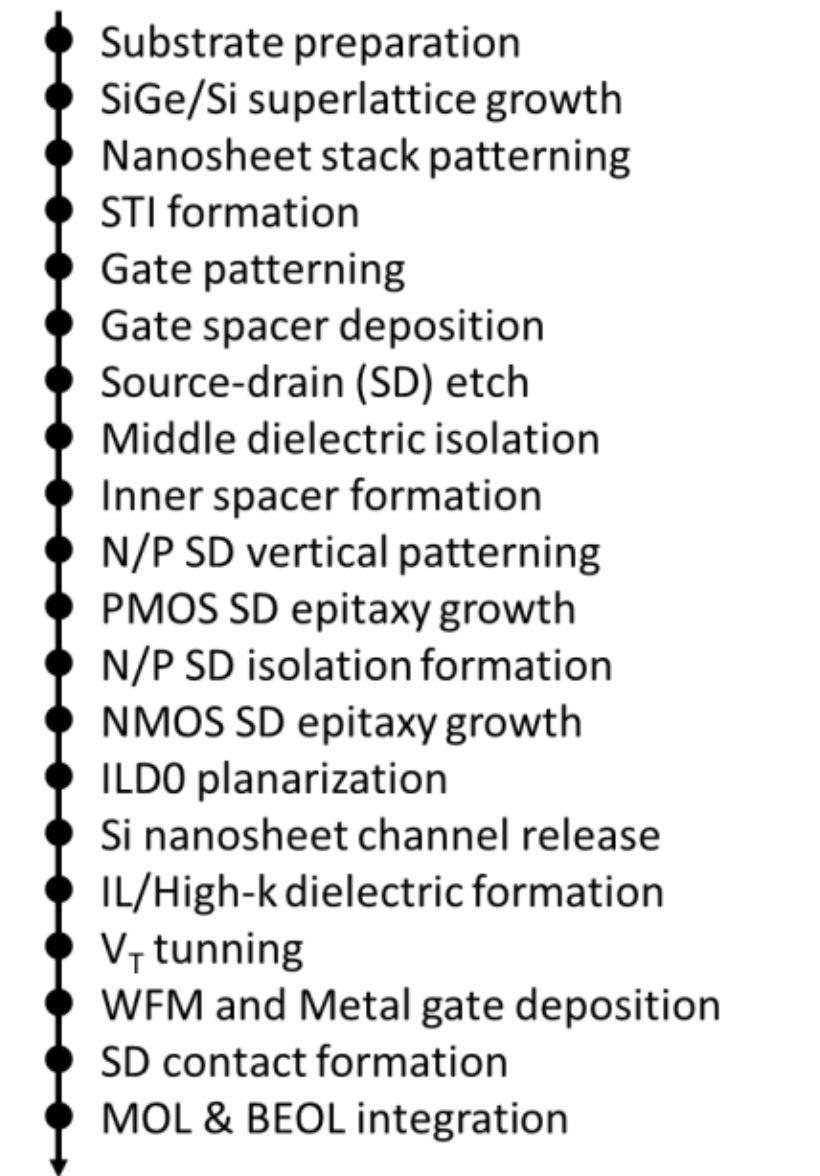

Sandy表示,她将提供制造过程的一些细节,“但不会太多”。这是一个 20 个步骤的流程,但显然每个步骤内都有许多子步骤。目前,该工艺的制造成本很高,她说工程师将及时解决这个问题,因此该工艺将具有价值。以下是 20 个步骤:

通过引入中间介质隔离、内部侧墙和n/p源漏隔离,垂直堆叠晶体管的存活率超过90%,并且具有高通态电流和低泄漏。有六个数量级 Ion/Ioff流动比率。

Sandy的结论:这仅仅是开始,还有很长的路要走。但大批量晶体管的情况不会比这更糟糕。我们需要努力生成具有更好特性的工艺特征、真正的良率电路。这只是一项为实用工艺架构铺平道路的研究,该架构可以推动未来逻辑技术、扩展和 PPAC 的进步。

编辑:芯智讯-浪客剑 来源:semiwiki