近日,比利时微电子研究中心(imec)宣布成功演示了高质量 300 毫米硅基量子点自旋量子比特处理,该设备在 1Hz 时产生具有统计意义的平均电荷噪声 0.6µeV/√ Hz。就噪声性能而言,所获得的值是在 300 毫米晶圆厂兼容平台上实现的最低电荷噪声值。如此低的噪声值可实现高保真量子比特控制,因为降低噪声对于保持量子相干性和高保真控制至关重要。通过在 300 毫米 Si MOS 量子点工艺上反复且可重复地演示这些值,这项工作使基于硅基量子点的大规模量子计算机成为现实。

硅基量子点自旋量子比特是实现大规模量子计算机的有前途的构建模块,主要有两个原因。首先,具有长量子相干时间(反映其长时间存储量子信息能力的指标)和高保真量子门操作的硅基自旋量子比特已在实验室环境中反复演示,因此是一种成熟且经过测试的技术,具有现实的前景。其次,对于长期可行性而言,可能更重要的是,底层技术与 CMOS 制造技术兼容且紧密相关,因此提供了晶圆级均匀性和良率的可能性,并且硅基量子点结构需要先进的后端互连,而这正是真正大规模量子芯片所必需的,其中数百万甚至数十亿个量子比特同步运行。

存在几种类型的硅基量子点自旋量子比特,imec 正在对其进行研究。在这项工作中,量子点自旋量子比特由金属氧化物半导体 (MOS) 量子点结构定义,这种结构类似于经过修改的晶体管结构,用于捕获电子或空穴的单个自旋。为了实现较长的量子相干时间,噪声(特别是量子点的电荷噪声)应尽可能低。该噪声通常来自残留电荷,这些电荷被捕获在量子点附近甚至内部,去除这些电荷是提高自旋量子比特性能的关键。最终,这取决于量子点量子比特结构的完整处理堆栈,因为需要尽量减少引入的任何缺陷。虽然这可以通过实验室技术(例如非常温和的剥离工艺)来实现,从而减少工艺损伤,但工业制造技术(如减法蚀刻和基于光刻的图案化)已被证明很容易导致设备和界面质量下降,特别是在量子点量子比特附近的 Si/SiO2 界面处。因此,在专业制造设施中制造的基于 Si/SiO2 的量子点结构的电荷噪声通常高于使用实验室处理获得的值。

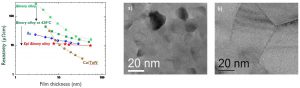

通过精心优化和设计 300 毫米 Si/SiO2 基 MOS 栅极堆栈,imec 在 300 毫米晶圆上实现了创纪录的低平均电荷噪声水平,仅为 0.6µeV/√ Hz(1Hz 时),并使用统计方法进行了表征。imec 研究员兼量子计算项目总监 Kristiaan De Greve:“我们展示了电荷噪声水平,与目前最先进的基于晶圆厂的 Si 量子点结构相比,噪声水平降低了半个数量级到一个数量级,并实现了非常均匀的量子点操作。我们的结果证实,300 毫米 Si MOS 是量子点自旋量子比特的有力材料平台,并凸显了量子比特开发工业制造技术的成熟度。”

此外,用于表征低电荷噪声设备的统计分析方法揭示了其起源的基本见解。“了解电荷噪声的来源将为我们提供进一步优化量子点结构的方向,”De Greve 补充道。“低噪声量子比特环境和 CMOS 制造的一致性只是一系列使能技术发展的开始,这些技术发展将使量子芯片升级为最终的实用量子计算,根据目前的理解,这将需要数百万个物理量子比特。”

编辑:芯智讯-林子