三星正在奋力冲刺3nm制程,希望借此进一步缩小与台积电的差距。最新的信息显示,三星旗下晶圆代工事业部门已和全球电子设计自动化(EDA)巨头Cadence合作推出了3nm制程相关开发工具,加速相关先进制程开发的软件程序。相较之下,台积电与EDA厂商于5月推出了3nm相关开发工具,三星正以三至四个月的差距紧追在后。

EDA工具在晶圆代工推进先进制程初期极具重要性,相关软件工具能减少IC设计客户设计的时间,能加速产品设计定案,让后续光罩制作、投片生产顺利展开,被业界视为先进制程能成功推进的关键因素之一。

业界形容,相关工具到位,等于先进制程开发进度已达约三分之一,后续在客制化应用推广将能更快速推进,不过,完成EDA设计之后,后续实际生产良率提升,以及客户接受度是另外两大重点。

因此,尽管三星在EDA阶段仅落后台积电三至四个月,但台积电在生产良率与客户伙伴关系更具优势,预料在3nm竞赛中,仍会维持霸主地位。

不过,需要指出的是,三星的3nm制程工艺采用了全新的环绕闸极技术(GAA)技术,与台积电鳍式场效电晶体FinFET架构的3nm制程完全不同,所以三星需要新的设计和认证工具。

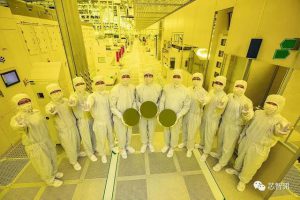

Cadence是在美国当地时间9月8日向三星晶圆代工部门提供3nm环绕闸极技术(GAA)代工相关的流程设计工具(PDK),进而在半导体设计、实施和物理验证方面提供比现有程序更快的解决方案。

Cadence研发副总裁Michael Jackson表示,这次与三星合作,开发出能够更有效地生成和验证半导体设计等的新流程,同时在新的合作计划下,可以期待在半导体生产中更稳定使用电力、提高性能等。

不过,需要指出的是,三星3nm GAA制程流片进度是与新思科技(Synopsys)合作,采用了新思科技的Fusion Design Platform。针对三星3nm GAA制程技术的物理设计套件(PDK)已在2019 年5 月发表,并2020 年通过制程技术认证。

半导体业界人士观察,若三星抢占GAA工艺量产的先机,将有机会成为吸引全球客户的有力武器。不过,台积电3nm架构仍以FinFET为基础,并非采用GAA架构量产,且台积电客户群远多于三星,也反映先投入GAA技术并非易事,三星则是押注在该架构来争取超越台积电。

三星与Cadence决定在数据中心、网络系统、第五代移动通讯(5G)相关半导体领域加快技术合作。据悉,对于开发设计系统,三星方面将提供相关大数据,冲刺3nm生产,目标达成明年下半年量产目标。

先前Cadence支持台积电5nm制程的PCIe 5.0 规格IP是在今年准备就绪。至于后续支持3nm制程的规格版本预计2022年初推出。而三星晶圆代工的进度也正计划追赶相关方向。

台积电已组成丰富的大同盟,和全球达到18家以上EDA大厂合作,而三星电子看到相关联盟优势,也正计划将加强各大美国EDA厂商合作,特别是在3nm相关技术在内的下一代半导体技术开发合作。

编辑:芯智讯-林子 来源:经济日报