当地时间6月16日,晶圆代工巨头台积电在美国加利福尼亚州圣克拉拉召开了2022年台积电技术研讨会,介绍了台积电的技术现状和即将推出的路线图,涵盖了工艺技术和先进封装开发的各个方面。

在之前的报道《台积电2nm细节曝光:功耗降低30%!成熟制程产能2025年将提升50%》当中,我们有介绍关于制程工艺技术的部分。今天我们再来聊聊台积电的先进封装技术。

一、台积电的3D Fabric产品组合

在2.5D和3D先进封装技术方面,台积电已经布局了超过10年。目前,台积电已将2.5D和3D先进封装相关技术整合为“3DFabric”平台,可让客户们自由选配,前段技术包含3D的整合芯片系统(SoIC InFO-3D),后段组装测试相关技术包含2D/2.5D的整合型扇出(InFO)以及2.5D的CoWoS系列家族。

从技术上来讲,SoC与“3D”高带宽内存 HBM 堆栈的 2.5D 集成已经是一个组合产品。如上所述,台积电设想未来将3D SoIC与2.5D CoWoS/InFO相结合,作为非常复杂的异构系统设计的一部分,实现更丰富的拓扑结构组合。

与研讨会上的工艺技术演示一样,台积电对其先进封装技术的更新非常简单 ——表明成功的、持续的路线图执行。下面将重点介绍几个代表新方向的具体领域。

特别值得注意的是台积电对高级系统集成工厂的投资,该工厂将支持3D Fabric产品,提供完整的组装和测试制造能力。

二、2.5D封装

有两类2.5D封装技术 - “片上晶圆基板”(CoWoS)和“集成扇出”(InFO)。

(请注意,在上图中,台积电将一些InFO产品表示为“2D”。)

这两种技术的关键举措是继续扩大最大封装尺寸,以便能够集成更多的芯片(和 HBM 堆栈)。例如,在硅转接板(CoWoS-S)上制造互连层需要“拼接”多个光刻曝光——目标是根据最大光罩尺寸的倍数增加转接板尺寸。

1、CoWoS系列

具体来说,CoWoS已经扩展到提供三种不同的转接板技术(CoWoS中的“晶圆”):

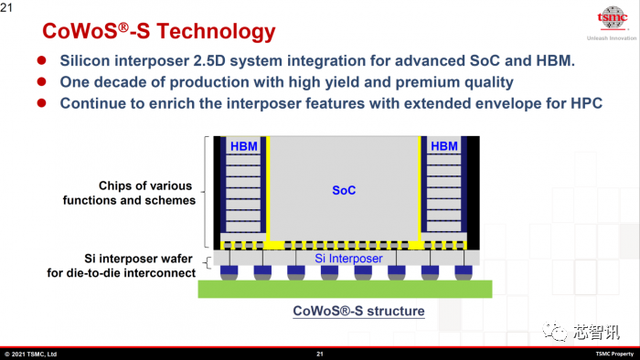

CoWoS-S

●采用硅中介层,基于现有硅片光刻和再分布层的加工

●自2012年开始批量生产,迄今为止为已向20多家客户提供了>100种产品

●转接板集成了嵌入式“沟槽”电容器

●目前最新的第五代CoWoS-S封装技术,将增加 3 倍的中介层面积、8 个 HBM2e 堆栈(容量高达 128 GB)、全新的硅通孔(TSV)解决方案、厚 CU 互连、第一代的eDTC1100(1100nF/mm²)、以及新的 TIM(Lid 封装)方案。

根据官方的数据,台积电第 5 代 CoWoS-S封装技术,有望将晶体管数量翻至第 3 代封装解决方案的 20 倍。

CoWoS-R

●使用有机转接板以降低成本

●多达 6 个互连的再分布层,2um/2um L/S

●4倍最大光罩尺寸,支持一个 SoC,在 55mmX55mm 封装中具有 2 个 HBM2 堆栈;最新开发中的方案拥有 2.1 倍最大光罩尺寸,支持2 个 SoC 和 2HBM2 采用 85mmX85mm 封装

CoWoS-L

●使用插入有机转接板中的小硅“桥”,用于相邻芯片边缘之间的高密度互连(0.4um/0.4um L/S 间距)

●2023年将会推出拥有2倍最大光罩尺寸大小,支持 2 个 SoC 和 6 个 HBM2 堆栈的方案;2024年将推出4倍最大光罩尺寸,可支持 12 个 HBM3 堆栈的方案。

台积电强调,他们正在与 HBM 标准小组合作,共同制定 CoWoS 实施的 HBM3 互连要求的物理配置。

HBM3 标准似乎已经确定了以下堆栈定义:4GB(带 4 个 8Gb 芯片)到 64GB(16 个 32Gb 芯片)的容量;1024 位信号接口;高达 819GBps 带宽。这些即将推出的具有多个 HBM3 堆栈的 CoWoS 配置将提供巨大的内存容量和带宽。

此外,由于预计即将推出的CoWoS设计将具有更大的功耗,台积电正在研究适当的冷却解决方案,包括改进芯片和封装之间的热界面材料(TIM),以及从空气冷却过渡到浸入式冷却。

2、InFO

在临时载体上精确(面朝下)放置后,芯片被封装在环氧树脂“晶圆”中。再分布互连层被添加到重建的晶圆表面。然后将封装凸块直接连接到再分配层。

有InFO_PoP、InFO_oS和InFO_B拓扑。

InFO_PoP

如下图所示,InFO_PoP表示封装对封装配置,专注于DRAM封装与基本逻辑芯片的集成。DRAM顶部芯片上的凸块利用贯穿InFO过孔(TIV)到达重新分配层。

InFO_PoP主要用于移动平台,自 2016 年以来,InFO_PoP出货量超过 12 亿台。

InFO_PoP存在的一个问题是,目前DRAM封装是定制设计,只能在台积电制造。不过,在开发中的还有另一种InFO_B方案,其中在顶部添加了现有的(LPDDR)DRAM封装,并且组件由外部合同制造商提供。

InFO_oS

InFO_oS(基板上)可以封装多个芯片,再分布层及其微凸起连接到带有TSV的基板。目前,InFO_oS投产已达5年以上,专注于HPC客户。

- 基板上有 5 个 RDL 层,2um/2um L/S

- 该基板可实现较大的封装尺寸,目前为110mm X 110mm,并计划实现更大的尺寸

- 拥有130um C4 凸块间距

InFO_M

InFO_M是InFO_oS的替代方案,具有多个封装芯片和再分布层,无需额外的基板 TSV(<500mm²封装,于2022年下半年投产)。

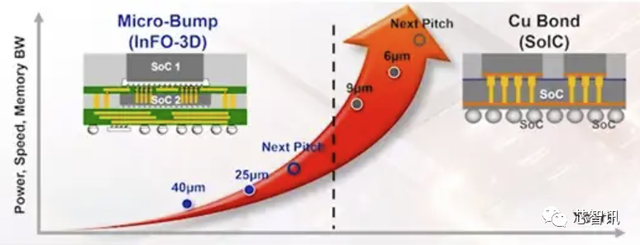

三、3D 封装

InFO-3D

是一种3D堆叠封装技术,该技术利用垂直集成的微凸块芯片与再分布层和TIF集成,专注于移动平台。

3D SoIC

更先进的垂直芯片堆叠3D拓扑封装系列被称为“系统级集成芯片”(SoIC)。它利用芯片之间的直接铜键合,具有侵略性的间距。

SoIC有两种产品——“wafer-on-wafer”(WOW)和“chip-on-wafer”(COW)。WOW拓扑在晶圆上集成了复杂的SoC芯片,提供深沟槽电容(DTC)结构,以实现最佳去耦。更通用的 COW 拓扑堆叠多个 SoC 芯片。

下表显示了符合SoIC组装条件的工艺制程节点。

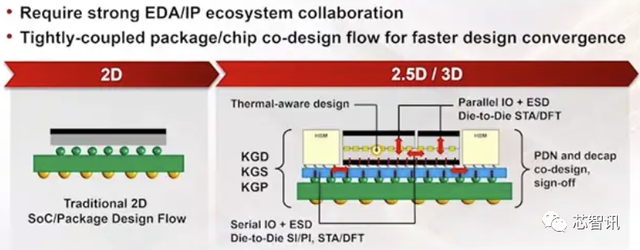

3DFabric(包括 3Dblox)的设计支持

如上图3D Fabric的右上角所示,台积电正在设想复杂的3D系统设计级封装实现,结合3D SoIC和2.5D技术。

如上所述,设计流程的复杂性非常大,需要高级热力、计时和SI/PI分析流程(也可以处理模型数据量)。

为了实现这些系统级设计的开发,台积电与EDA供应商合作开展了三项主要的设计流程计划:

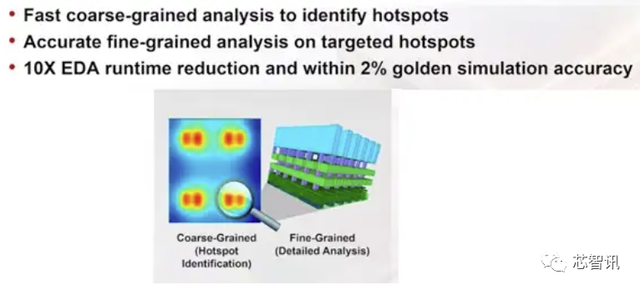

●改进的热分析,使用粗粒度加细粒度方法

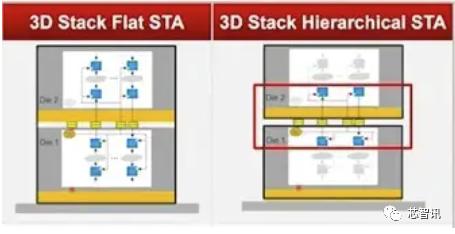

●分层静态时序分析

单个模具由抽象模型表示,以降低总(多角)数据分析的复杂性

●前端设计分区

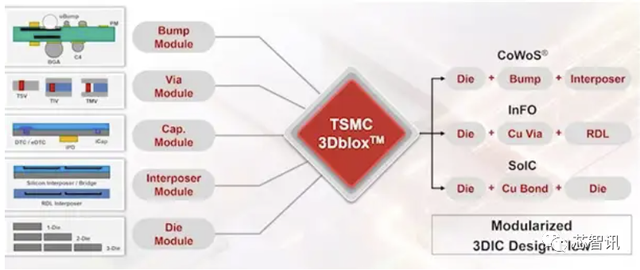

为了帮助加速复杂系统的前端设计分区,台积电采取了一项名为“3Dblox”的举措。

目标是将整个物理封装系统分解为模块化组件,然后进行集成。模块类别包括:

- bumps/bonds

- vias

- caps

- interposers

- die

这些模块将被整合到任何SoIC、CoWoS或InFO封装技术中。

特别值得注意的是,台积电正在努力使3D Fabric设计能够使用各种EDA工具,即使用一个EDA供应商工具完成物理设计,并(可能)使用不同的EDA供应商产品来支持时序分析,信号完整性/功率完整性分析,热分析。

3Dblox似乎将SoC的“参考流”概念提升到一个新的水平,台积电推动了EDA供应商数据模型和格式之间的互操作性。整体3Dblox流量能力将于2022年第三季度推出。(初步步骤,即在InFO上自动路由再分配信号,将是发布的第一个功能。)

显然,台积电正在广泛投资于先进的封装技术开发和(特别是)新的制造设施,因为2.5D和3D配置的预期增长。从 HBM2/2e 到 HBM3 内存堆栈的过渡将为采用 CoWoS 2.5 技术的系统设计带来可观的性能优势。移动平台客户将扩大InFO多芯片设计的多样性。毫无疑问,采用结合3D和2.5D技术的复杂3DFabric设计也将增加,利用台积电“模块化”设计元素以加速系统分区的努力,以及他们为应用广泛的EDA工具/流程所做的努力。

编辑:芯智讯-浪客剑

编译自:

https://semiwiki.com/semiconductor-manufacturers/tsmc/314439-tsmc-2022-technology-symposium-review-advanced-packaging-development/