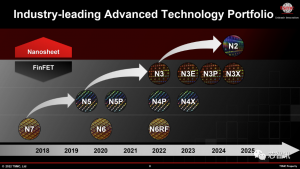

2023年1月3日消息,据Semiwiki报道,台积电在 2022 年 IEDM 上发表了两篇关于 3nm 的论文:“关键工艺特性可实现3nm CMOS及更高技术的激进接触栅极间距缩放”和“3nm CMOS FinFlex为移动SOC和高性能计算应用提供增强的能效和性能的平台技术”。

Semiwiki的编辑表示,第一篇论文描述了台积电的 N3 工艺,第二篇论文描述了台积电 N3E 工艺,这在第二次演讲中得到了演讲者的证实。

另据Business Next的报道,目前台积电的3nm良率可能高达75%至80%。

台积电N3

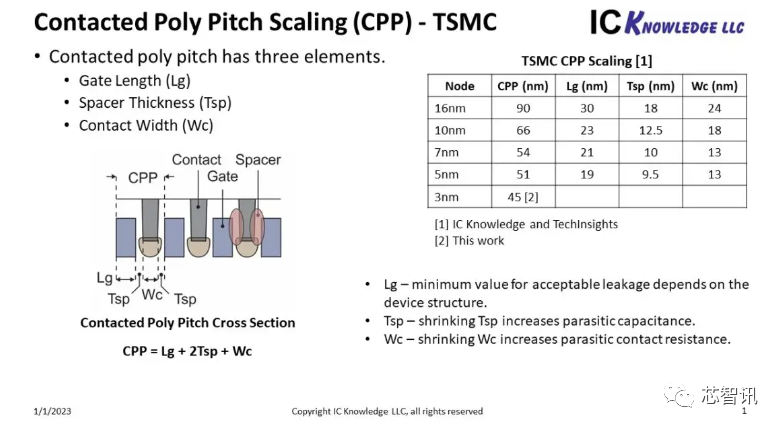

在第一篇论文中,台积电公开了45nm的接触栅极间距(Contacted Gate Pitch,CPP)。CPP 由栅极长度 (Lg)、接触间隔厚度 (Tsp) 和接触宽度 (Wc) 组成,如图 1 所示。

△图1,CPP

从图 1 中,我们可以看到台积电通过减少构成 CPP 的所有三个元素来减少每个新节点的 CPP。逻辑设计是通过使用标准单元完成的,CPP 是标准单元宽度的主要驱动因素,因此缩小 CPP 是提高新节点密度的关键部分。

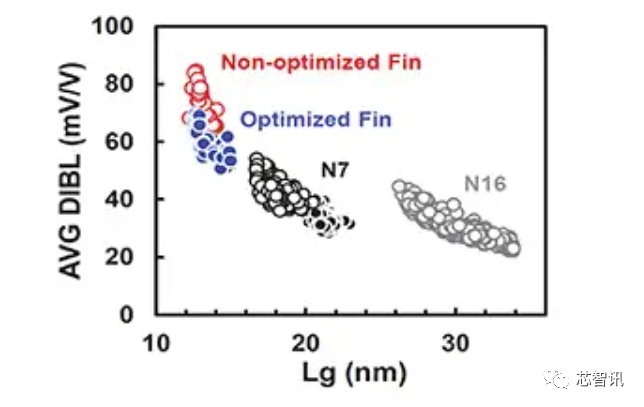

最小 Lg 是通道栅极控制的函数,例如,从通道厚度不受约束的单栅极平面器件转变为具有 3 个栅极围绕薄通道的 FinFET,从而实现较短的 Lg。图 2 说明了多个台积电节点的 DIBL 与 Lg 对比,以及优化鳍片如何降低当前工作的 DIBL。

△图2,DIBL 与 Lg。

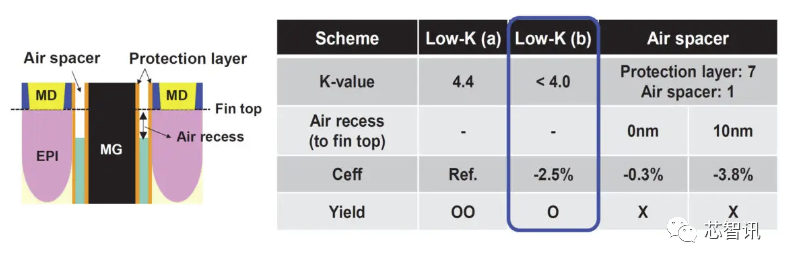

收缩CPP的第二个因素是Tsp厚度。降低Tsp会增加寄生电容,除非对垫片进行优化以降低k值。图3显示了台积电对低k间隔物与气隙间隔物的研究。台积电发现,低k间隔物是扩大CPP的最佳解决方案。

△图 3,与栅极间隔物的接触。

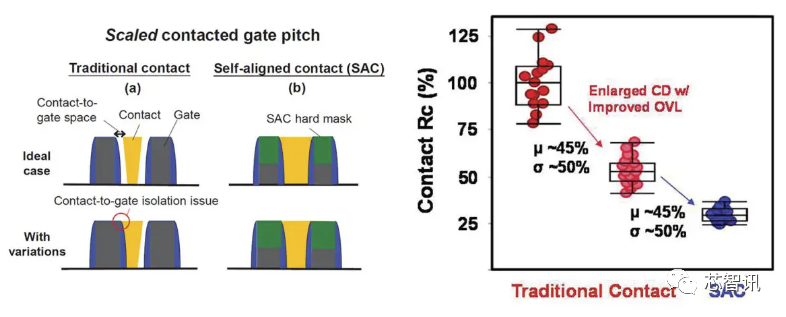

CPP的最后一个要素是接触宽度。在这项工作中,台积电开发了一种优化的自对准接触(SAC)方案,该方案提供了较低的接触电阻。图4的左侧显示了SAC,右侧显示了电阻的改善。

△图4,自对准触点

这项工作使N3工艺具有0.0199μm²的高密度SRAM尺寸。随着台积电推进其2nm工艺,这项工作也很重要。在2nm处,台积电将转向一种称为水平纳米片(HNS)的环绕栅极(GAA)架构,HNS可实现更短的Lg(4个栅极,而不是围绕薄栅极的3个栅极),但Wc和Tsp仍需要优化。

台积电N3E

台积电将N3E工艺描述为N3的增强版本,有趣的是,N3E被认为实现了与N3相比更宽松的间距,例如CPP,M0和M1都被认为出于性能和良率的原因而被放松。关于台积电N3以及是否准时,有不同的故事。Semiwiki的编辑认为,N5在2019年开始进入风险,到2020年圣诞节,苹果iPhone已经配备了N5芯片。N3 在 2021 年进入风险开始,iPhone 要到明年才会推出 N3 芯片。这个过程至少晚了 6 个月。在本文中,高密度SRAM单元尺寸为0.021μm²被披露。大于 0.0199 μm² 的 N3 SRAM 单元。N3的良率通常被描述为良好,其中提到了良率在60%至80%。

本文讨论此过程有两个主要特征:

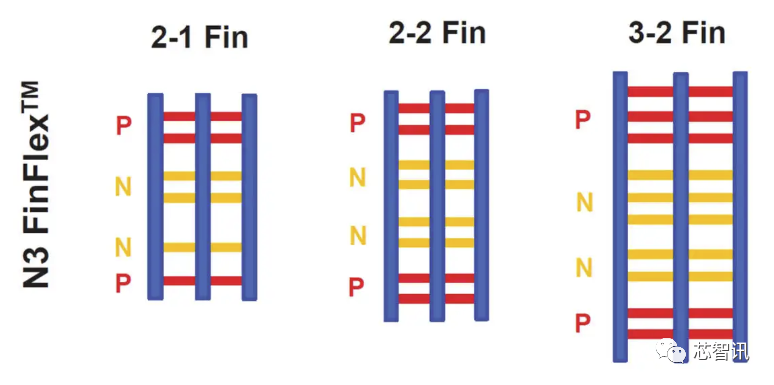

- FinFlex

- 最小金属间距为 23 纳米,铜互连采用“创新”衬里以实现低电阻

△图 5,FinFlex cell

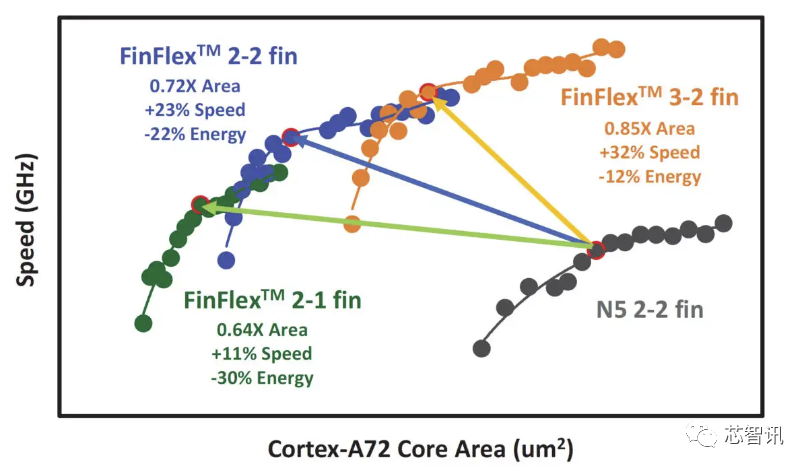

△图6,3nm FinFlex性能与 5nm的比较。

上图是大约 550 欧姆的 15 级金属堆栈的通孔电阻分布。在当前的工艺中,电源通过金属堆栈的顶部进入,并且必须通过通孔链向下到达设备,电源线中的电阻为550欧姆。这就是为什么英特尔、三星和台积电都宣布了其 2nm 级工艺采用背面供电。通过极端的晶圆减薄,从背面引入电源的过孔应该会使通孔电阻提高>10倍。

比较

作为读者,您可能会遇到的一个问题是,台积电3nm工艺与三星的3nm工艺相比如何。台积电仍在使用FinFET技术,而三星已经过渡到GAA——他们称之为多桥HNS。

根据计算,在5nm工艺节点,台积电最密集的逻辑单元密度是三星最密集逻辑单元密度的1.30倍。如果您查看图 6 中的台积电密度值,2-2 鳍式单元的密度比 5nm 中的 2-2 个鳍式单元密度高 1.39 倍,而 2-1 单元的密度提高了 1.56 倍。三星有两个版本的3nm,SF3E(3GAE)版本比5nm密度高1.19倍,SF3(3GAP)版本密度比5nm高1.35倍,进一步落后于台积电行业领先的密度。我也相信台积电在3nm上具有更好的性能和稍好的功率,尽管三星可能由于HNS工艺而缩小了功率差距。

编辑:芯智讯-浪客剑