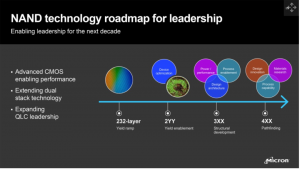

6月12日消息,日本半导体设备大厂东京电子(TEL)宣布,其等离子体蚀刻系统的开发和制造基地已经开发出一种创新的通孔蚀刻技术,可以用于堆叠超过400层的先进3D NAND Flash闪存芯片。开发团队的新工艺首次将电介质蚀刻应用带入低温范围,从而打造了一个具有极高蚀刻率的系统。

据介绍,这项创新的技术不仅能在短短33分钟内完成10微米深度的高纵横比蚀刻,缩减了耗时,而且蚀刻结构的几何形状相当明显,也有助于制造更高容量的3D NAND闪存芯片。

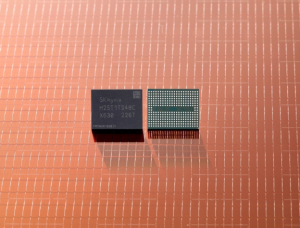

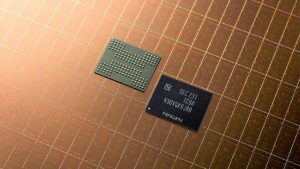

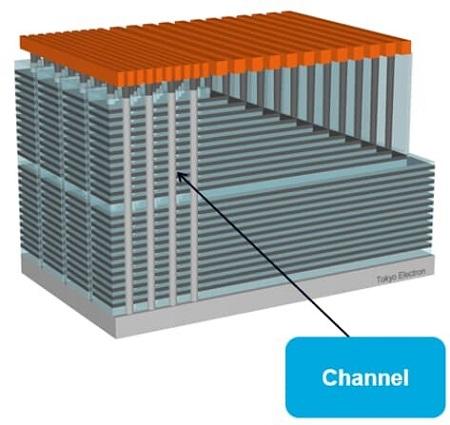

东京电子还提供了蚀刻后的相关图像,展示了开发的成果。其中包括显示了蚀刻后通孔图案的横截面SEM图像,以及孔底的FIB切割图像,另外还有东京电子的3D NAND闪存芯片的一个案例。

东京电子预告称,开发该项技术的团队将于2023年6月11日至6月16日,在京都举行的2023年超大规模集成电路技术和电路研讨会(2023 VLSI)上发表最新的研究成果报告。据悉,VLSI是最负盛名的国际半导体研究会议之一,利用这一机会,东京电子将展示为半导体技术创新和全球环境所做的努力。

值得一提的是,今年也是东京电子成立60周年。东京电子认为这是一个新的转型点,迎接未来的新挑战,继续为社会发展作出贡献。

编辑:芯智讯-林子

0