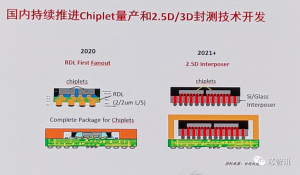

过去数十年来,为了芯片的晶体管数量以推升计算性能,半导体制造技术已从1971年10,000nm制程升级至2022年3nm制程,逐渐逼近目前已知的物理极限。但随着人工智能、AIGC等相关应用高速发展,设备端对于核心芯片的性能需求将越来越高;在制程技术提升可能遭遇瓶颈,但是对算力需求持续走高的情况下,通过2.5D/3D先进封装技术提升芯片内部晶体管数量就显得格外重要。

半导体先进封装技术

这两年“先进封装”被聊得很多,封装大概可以理解为对芯片裸片的保护,保护电路芯片免受外界环境的不良影响。当然芯片封装还涉及到固定、散热增强,以及与外界的电气、信号互连等问题。而“先进封装”的核心还在“先进”二字上,主要是针对先进制程晶圆的封装技术。然而,人工智能浪潮下,带动AI服务器需求增长,也带动对于英伟达或AMD的AI加速芯片的需求,而这些AI加速芯片基本都采用了台积电的CoWoS先进封装产能供不应求,那究竟什么是CoWoS?

什么是CoWoS?

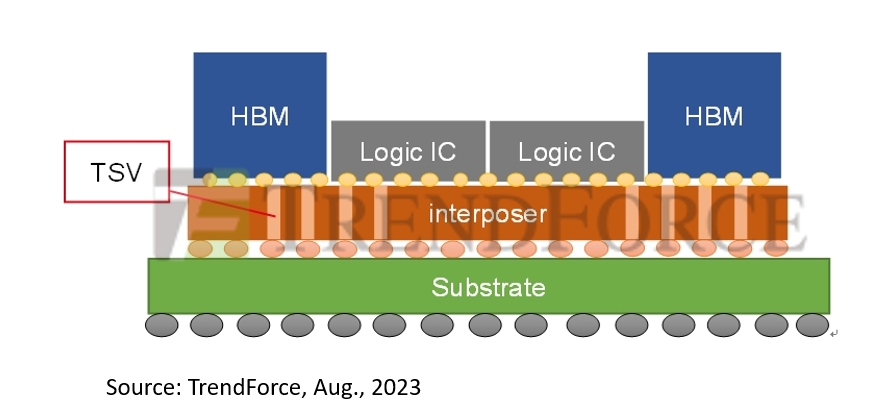

CoWoS是一种2.5D、3D的封装技术,可以分成“CoW”和“WoS”来看。“CoW(Chip-on-Wafer)”是芯片堆叠;“WoS(Wafer-on-Substrate)”则是将芯片堆叠在基板上。CoWoS就是把芯片堆叠起来,再封装于基板上,最终形成2.5D、3D的型态,可以减少芯片的空间,同时还减少功耗和成本。下图为CoWoS封装示意图,将逻辑芯片及HBM(高带宽內存)先连接于中介板上,桶过中介板内微小金属线来整合左右不同芯片的电子信号,同时经由“硅通孔(TSV)”技术来连接下方基板,最终通过金属球衔接至外部电路。

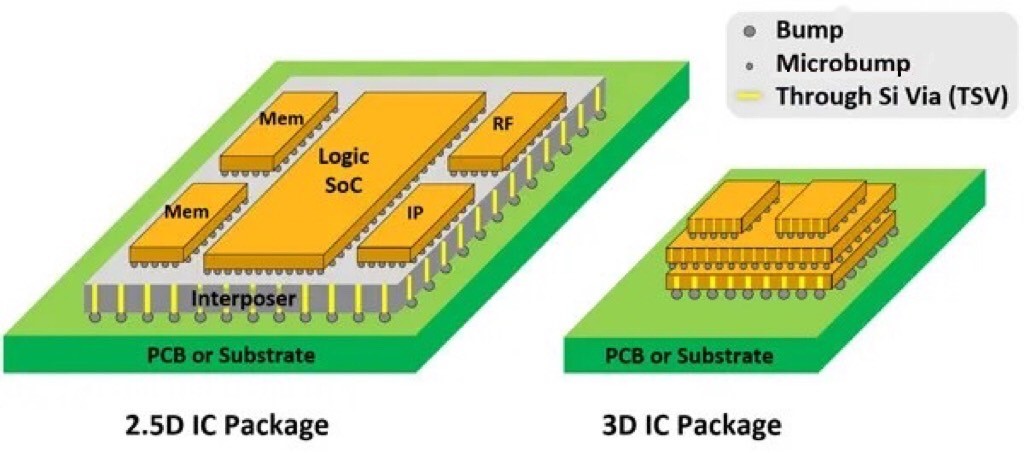

而2.5D与3D封装技术则是差别在堆叠方式。2.5D封装是指将芯片堆叠于中介层之上或透过硅桥连接芯片,以水平堆叠的方式,主要应用于拼接逻辑运算芯片和高带宽內存;3D封装则是垂直堆叠芯片的技术,主要面向高效能逻辑芯片、SoC制造。

▲2.5D和3D封装的差异(图片来源:Ansys)

先进封装,但不在封装厂完成!

说到先进封装,首先想到的会是台积电而非传统封测大厂,因为先进封装已经面临到7nm以下,而传统封装厂研发速度已无法跟进晶圆制程的脚步,其中CoWoS中的CoW部分过于精密,只能由台积电制造,所以才会造成产能供不应求的景象。同时,台积电拥有许多全世界的高阶客户,为此“一条龙”的服务更能同时维持制程与封装部分的良率,未来面对高阶客户的交付工作也将更为极致。

CoWoS的应用发展

高阶芯片走向多个小芯片、內存,堆叠成为必然发展趋势,CoWoS封装技术应用的领域广泛,包含高性能运算HPC、AI人工智能、数据中心、5G、物联网、车用电子等等,可以说在未来的各大趋势,CoWoS封装技术会扮演着相当重要的地位。

过去的芯片性能都依赖半导体制程的改进而提升,但随着元件尺寸越来越接近物理极限,芯片微缩难度越来越高,要保持小体积、高性能的芯片设计,半导体产业不仅持续发展先进制程,同时也朝芯片构架着手改进,让芯片从原先的单层,转向多层堆叠。也正因为如此,先进封装也成为延续摩尔定律的关键推手之一,在半导体产业中引领浪潮。

编辑:芯智讯-浪客剑 来源:Technews