近日,全球知名的EDA工具厂商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先进工艺的良率学习平台设计取得了重大突破,这将为三星后续5nm、4nm、3nm工艺的量产和良品率的提升奠定坚实基础。

周所周知,随着半导体制程工艺的不断推进,晶体管的大小也越来越逼近物理极限,芯片的设计和生产也变得更加的复杂,良率的提升也越来越困难。因此要想提高芯片的良率,就需要对各个环节进行细致的分析。

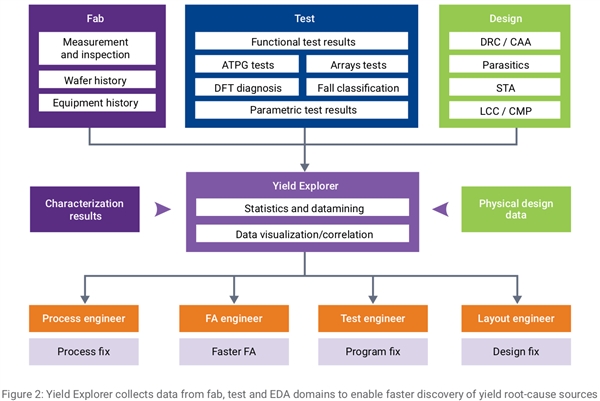

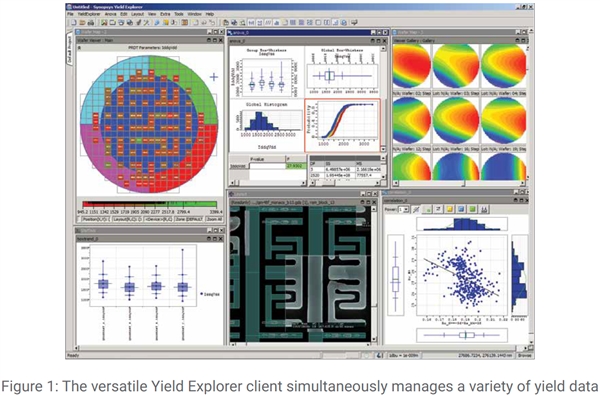

为此新思科技打造了量产探索平台(Yield Explorer),这是一种复杂的芯片量产良品率学习平台,可用来分析芯片设计、晶圆厂生产、产品测试三大方面的数据,以便帮助工程师找到缺点、改进良品率、提高产能。

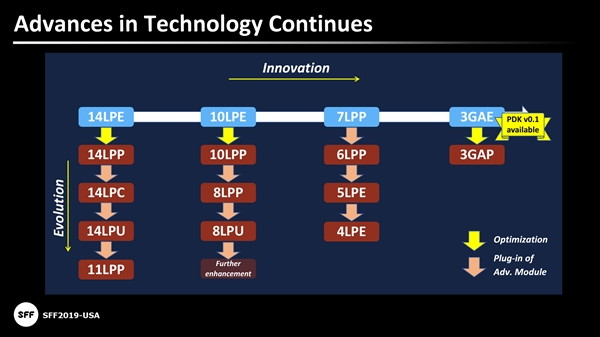

根据此前三星公布的路线图显示,三星工艺近期有14nm、10nm、7nm、3nm三个重要节点,其中14nm会演化出11nm,10nm会演化出8nm,7nm则会演化出6nm、5nm、4nm。

而每种工艺往往又会根据性能、功耗的不同而分为多个版本,比如14nm分成了14LPE、14LPP、14LPC、14LPU,3nm则分成3GAE、3GAP,预计会采用全新的材料。

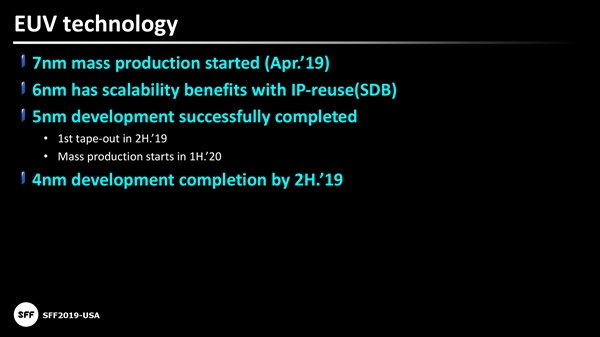

不久前,在三星在韩国举行的晶圆代工制造论坛上,负责晶圆代工业务的三星副总裁Jung Eun-seung对外公布了三星在半导体制造工艺上的进展。他透露,三星7nm EUV工艺将于2020年1月份量产。此外他还透露三星目前已经完成了5nm FinFET工艺的技术研发,有望在2020年上半年进入量产。4nm则将在今年下半年完成开发,新思的新平台将在其中发挥巨大作用。

再之后的重大节点就是3nm了,三星此前宣布3nm节点将使用GAA环绕栅极晶体管技术,三星通过使用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,主要取代FinFET晶体管技术。

编辑:芯智讯-林子