近日,比利时微电子研究中心(imec)于国际光学工程学会(SPIE)举行的先进光刻成形技术会议上,展示其High-NA(高数值孔径)光刻技术的重大进展,包含显影与蚀刻制程开发、新兴光刻胶与涂底材料测试、以及量测与光罩技术优化。imec与台积电、英特尔等国际大厂有密切合作,业界预期先进制程在2025年之后将进入埃米(angstorm)时代,High-NA技术将是量产关键。

High-NA光刻技术将是延续摩尔定律的关键,推动2nm以下的晶体管微缩。imec致力于打造High-NA光刻生态系统,持续筹备与极紫外光(EUV)光刻设备制造商阿斯麦(ASML)共同成立High-NA实验室。该实验室将会聚焦全球首台0.55 High-NA EUV微影设备的原型机开发。

imec执行长Luc Van den hove表示,imec与ASML合作开发High-NA技术,ASML现在正在发展首台0.55 High-NA EUV光刻设备EXE:5000系统的原型机。与现有的EUV系统相比,High-NA EUV光刻设备预计将能在减少曝光显影次数的情况下,实现2nm以下逻辑芯片的关键特征图案化。

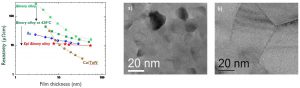

为了建立首台High-NA EUV原型系统,imec持续提升当前0.33 NA EUV光刻技术的投影解析度,借此预测光刻胶涂布薄化后的成像表现,以实现微缩化线宽、导线间距与接点的精密图案转移。同时,imec携手材料供应商一同展示新兴光刻胶与涂底材料的测试结果,在High-NA制程中成功达到优异的成像品质。同时也提出新制程专用的显影与蚀刻解决方案,以减少光刻图案的缺陷与随机损坏。

针对22nm导线间距或线宽的光刻应用,imec已经模拟了EUV光罩缺陷所带来的影响,包含多层光罩结构的侧壁波纹缺陷,以及光吸收层的线边缘粗糙现象。imec先进光刻技术研究计划负责人Kurt Ronse表示,这些研究成果让业界了解High-NA EUV光刻制程所需的光罩规格。

此外,通过与ASML和材料供应商合作,imec针对负责定义图案结构的光罩吸收层开发了新兴的材料与架构。

编辑:芯智讯-林子