当地时间6月16日,晶圆代工巨头台积电在北美召开了2022年台积电技术研讨会。不仅公布了台积电下一代的2nm制程技术的部分细节信息,同时还透露,通过在中国台湾、中国大陆和日本建设新晶圆厂或扩产,预计到2025年,台积电的成熟制程的产能将扩大约50%。

台积电2nm工艺细节曝光:功耗降低30%,2025年量产

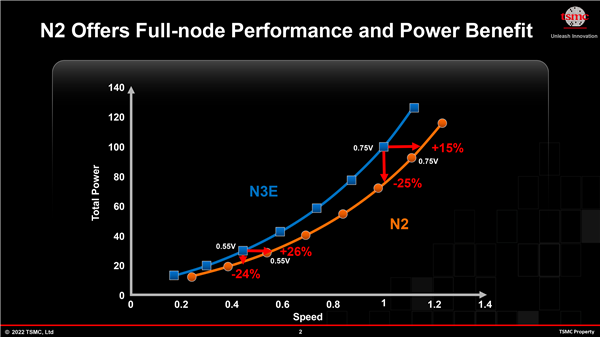

在此次2022年台积电技术论坛上,台积电首度公布了其下一代先进制程N2(即2nm制程)的部分技术指标:相较于其N3E(3nm的低成本版)工艺,在相同功耗下,台积电2nm工艺的性能将提升10~15%;而在相同性能下,台积电2nm工艺的功耗将降低23~30%;晶体管密度仅提升了10%。

需要指出的是,台积电N3E制程的晶体密度似乎要比N3(3nm)减少约8%,但仍比台积电N5(5nm)提升了30%,其优势在于,相比N3减少了4层EUV 光罩,使N3e将成为台积电更具成本及生产效率优势的重要节点。

这也是为什么,台积电N2相比N3E所带来的性能的提升幅度和功耗降低的幅度,均低于N3E相比N5的提升。

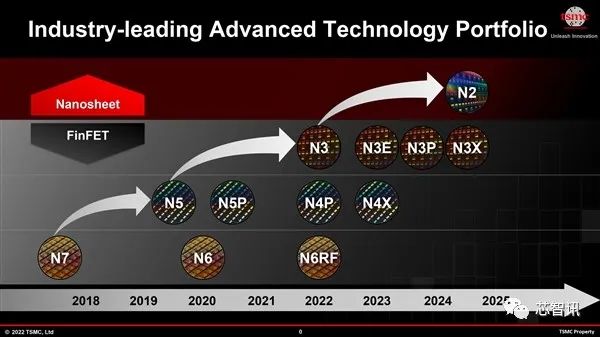

在晶体管架构方面,台积电N2终于抛弃了FinFET(鳍式场效应晶体管),采用了全新的纳米片晶体管架构(Nanosheet),即台积电版的GAAFET(环绕栅极晶体管)。

台积电还表示,N2不仅有面向移动处理器的标准工艺,还会有针对高性能计算和芯粒(Chiplet)的整合方案。

量产时间方面,根据台积电的规划,N2制程将于2025年量产。按照这个进度,英特尔或将在2nm工艺上实现对于台积电的赶超。此前,英特尔已宣布将会在2024年量产Intel 20A工艺,随后,英特尔又宣布其Intel 18A工艺也将提前到2024年量产。

另外,根据台积电最新展示技术路线图显示,在今年下半年台积电第一代3nm(N3)工艺量产之后,除了将推出低成本、低能耗的N3E之外,还将会推出高性能版本的N3P,以及性能和功耗均更具优势的N3X。

成熟制程产能提升50%

虽然目前智能手机、PC、服务器等领域都需要先进制程的处理器,但同时也仍然会用到大量的成熟制程芯片。同时,很多家电、物联网设备更是大量依赖成熟制程的芯片。

根据台积电以智能手机为例公布的数据显示,对于目前的5G智能手机来说,存在着非常多的成熟制程芯片,比如各种传感器(包括MEMS传感器和图像传感器)大概会有10~25颗,制程工艺涵盖0.35μm~28nm;音频/显示/触控芯片,大约会有2~4颗,制程工艺涵盖90nm~22nm;射频芯片大约会有15~40颗,制程工艺涵盖65nm~6nm;电源管理相关芯片大约会有10~30颗,制程工艺涵盖025μm~40nm。

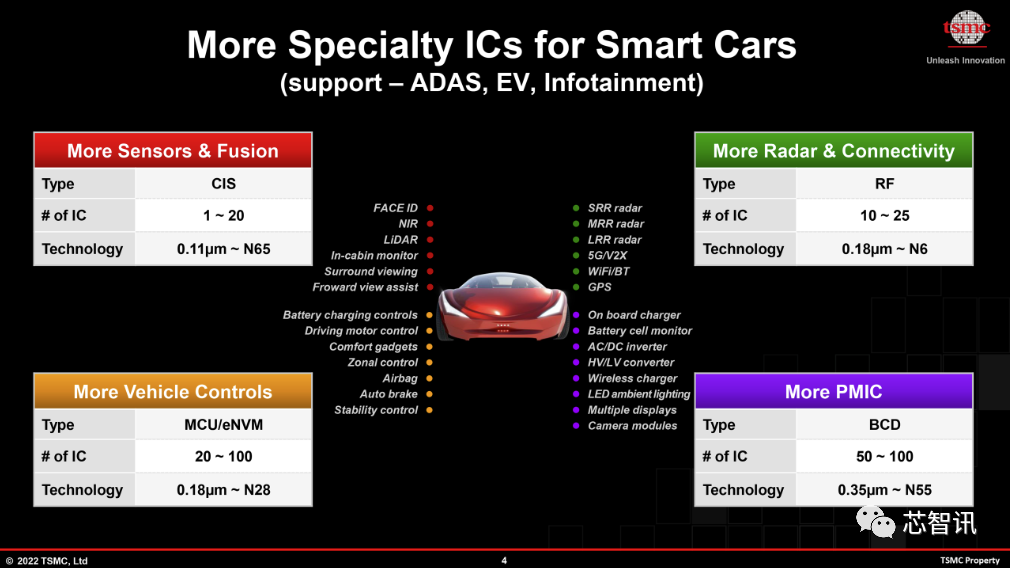

此外,汽车市场对于成熟制程的芯片需求也在持续爆发,特别是随着汽车电动化、智能化、联网化、自动化,每辆汽车最少也需要数百颗芯片。而这其中,大部分都是成熟制程芯片。

比如在感知方面,可能会用到1-20颗的图像传感器芯片,制程工艺可能会在0.11μm~65nm;在雷达和连接性方面,可能会用到10~25颗芯片,制程工艺涵盖0.16μm-6nm;在车辆控制方面,可能会用到20~100颗的MCU及eNVM芯片,制程工艺涵盖0.18um ~ 28nm;在电源管理方面,将会用到大约50-100颗BCD芯片,制程工艺涵盖0.35~55nm。

另外,有数据预测,数年后,每辆汽车需要的芯片数量将超过1500颗。

虽然,台积电在先进制程技术及产能上全球领先,同时先进制程也是台积电营收的最大来源。但是面对庞大的成熟制程芯片的需求,特别是自2020年四季度爆发的成熟制程芯片产能的持续紧缺,也推动了包括台积电在内的众多晶圆代工/IDM厂商持续扩大成熟制程产能。

在此次技术研讨会上,台积电再度提及了其为了提升成熟及特殊制程的四项投资计划:

1、日本九州熊本Fab 23 第一期建设,使用台积电N12、N16、N22 和N28 节点生产芯片,届时每月有高达45,000 片12吋晶圆的生产能力。后续还将提升至每月5.5万片。

2、台湾台南Fab 14 第八期。

3、台湾高雄Fab 22 第二期。

4、南京Fab 16 第1B 期,台积电当地生产N28 节点制程芯片,量产后产能将达每月4万片28nm。不过有传言表示,新阶段产能将采用更先进节点生产芯片(台积电南京厂原本就有生产16/12nm工艺)。

据台积电介绍,预计三年内,将让成熟及特殊节点产能提高50%。这对台积电来说是重大转变,同时将提高台积电的竞争优势。

在2021年之前,台积电一直没有扩大其成熟制程的产能,这也使得其成熟制程的营收占比持续下滑。根据台积电今年一季度的财报显示,目前16-5nm制程的营收占比约为64%,成熟制程的营收占比仅36%。

如果到2025年,台积电的成熟及特殊节点产能提升50%,那么或将推动其成熟制程的营收占比的大幅回升。同时,这也将对于联电、格芯、中芯国际等依赖于成熟制程的竞争对手带来一定的压力。

发展通用IP机制

在持续推进先进制程,以及提升成熟与特殊制程产能同时,台积电也在积极发展通用IP机制,以使满足一些客户希望在新的制程工艺下重新使用以前为运算或RF射频开发的IP。

通用IP机制还有其他的一些优势。比如台积电N6RF 制程,允许芯片设计人员将高性能逻辑芯片与RF 射频结合,构建基带芯片等产品或其他更特殊的解决方案。这是在许多客户都熟悉台积电N6 节点制程情况下,更有机会将RF功能整合到其他高性能产品,格芯也有类似做法。

编辑:芯智讯-浪客剑