7月14日消息,根据外媒报导,IBM与日本半导体设备大厂东京电子于近日宣布,在3D芯片堆叠方面获得了新得技术突破,成功运用了一种新技术将3D芯片堆叠技术用于的12 吋晶圆上。由于芯片堆叠目前仅用于高阶半导体产品,例如高带宽内存(HBM) 的生产。不过,在IBM 与东京电子提出新的技术之后,有机会扩大3D芯片堆叠技术的应用。

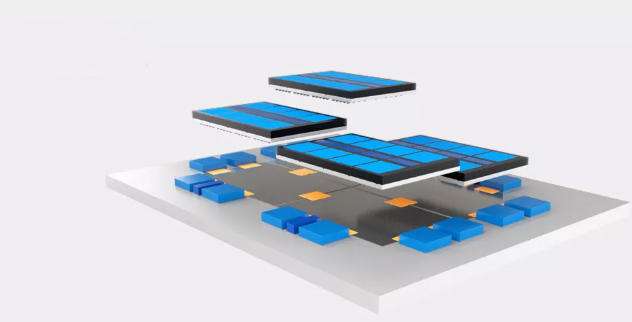

据报导称,3D芯片堆叠技术在当前被视为延续摩尔定律(Moore\'s Law) 的利器之一,这使得不少头部的半导体企业都在进行努力,期望将评价芯片制造技术的指标由“每单位面积下的晶体管数量”,转变为“每单位体积下的晶体管数量”。而与一般平面结构的芯片相较,3D芯片堆叠允许多层堆叠,而硅通孔封装(TSV) 就是3D芯片堆叠技术当中的关键。

IBM 与东京电子新开发的技术,本质上是一种将硅芯片连接在一起的新方法。传统的芯片堆叠需要通过硅通孔技术来实现,这可以使得电力向上流入堆叠层,并使两层串联执行工作。但是,这需要削减堆叠层的背面,以露出TSV 空间以提供另一层堆叠层透过TSV 来连结。只是,堆叠层中的厚度非常薄,通常仅小于100 微米。这就意味着它们非常的脆弱,所以他们当中需要一个载体来支撑。

通常这些载体芯片由玻璃制成。所以,借助载体与晶圆键合,以确保它可以在生产过程中不受损坏。完成生产后,使用紫外镭射去除载体。在某些情况下,也可以继续使用载体,但将其进行层与层分离需要物理的机械力来帮助,这对于晶圆的完整性可能会造成风险。

而IBM 与东京电子新开发的技术,将使用红外线镭射来进行层与层分离,进一步剥离两个对硅通孔的芯片,将能有效的降低破坏晶片完整性的风险。

另外,新技术也将允许在不使用玻璃载体的情况下堆叠两个硅芯片。相反,制造商可以跳过这一步,直接进入硅晶圆跟晶圆连接堆叠的步骤。IBM 表示,该技术除了不再需要这个额外步骤来简化流程之外,还有其他优势。例如,它将有助于消除工具兼容性的问题,及降低缺陷的风险之外,还允许对薄晶圆进行线上测试。IBM 指出,这些优势将使先进的小晶片结构生产变为简易,也使得其技术可以广泛的被应用。

报导强调、自2018 年以来,IBM 和东京电子在该项技术的研究已经有一段时间了。有鉴于晶圆制造的发展方向,这可能会是该产业的一个关键发展。因为,随着节点尺寸的微缩到2纳米以下,封装和堆叠技术将成为将继续提升芯片性能的一项技术。比如,处理器大厂英特尔已经在发展使用其Foveros 3D技术为其Meteor Lake 系列处理器进行3D 芯片堆叠设计。不过,相较于英特尔,竞争对手AMD 在这方面更是早已运用。然而,到目前为止,AMD 的Zen 3 架构的处理器仅在其处理器上堆叠L3 缓存。有传言表示,AMD 将会在Zen 4 架构的处理器上,以及所谓的Raphael-X 的系列产品中,采用3D 芯片堆叠技术。有消息显示,AMD即将推出的RDNA3 GPU 也可能会采用。

IBM 表示,它已在美国纽约州建立了一个新的研发与测试据点,用以研究该项新新技术,而且未来它将扩大其规模。IBM 的目标就是使用该技术创建一个完整的3D 晶片堆叠。如此,这将有助于解决供应链问题,同时也可以提高绩效。IBM 预计新技术将能帮助半导体供应链降低所需生产与使用的产品数量,同时也有助于未来几年运算处理能力的提升。

编辑:芯智讯-林子 来源:Technews