新产品亮相 统一的硬件仿真与原型验证系统

不断发展的SoC和Chiplet芯片创新,使芯片规模不断扩大,系统验证时间不断增加,对高性能硬件验证系统提出了更多的需求,包括虚拟或物理验证、深度调试、提前软件开发等,这些需求往往需要切换多种EDA工具配合完成,不仅存在重复劳动或者耗费人力进行转换的问题,也导致了数据的碎片化,降低了验证重用的可能性,大大降低了验证效率。

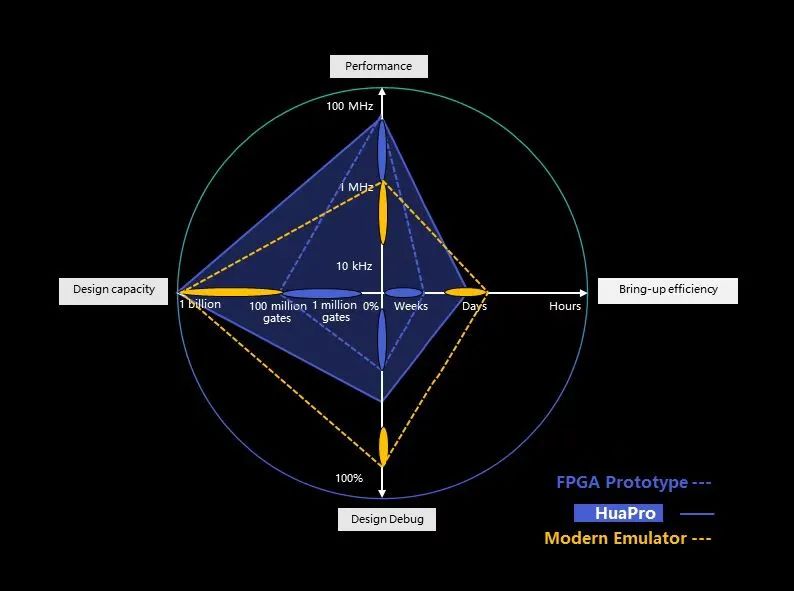

作为新一代FPGA双模验证系统,桦捷HuaPro P2E通过统一软硬件平台支持硬件仿真与原型验证双工作模式,帮助开发团队突破了传统软硬件验证工具的割裂限制。这得益于芯华章自主研发的一体化、全自动HPE Compiler,支持大规模设计的自动综合、智能分割、优化实现,并支持深度调试、无限量、任意深度的信号波形采集、动态触发、内存加载和读取等多种调试能力。

-

单个FPGA上多达36个PHC的丰富互连接口 -

FPGA互连IO性能支持单端1.6Gbps,达到业界最高水平 -

丰富的高速SERDES接口达24Gbps -

数十种接口验证子卡,并支持FMC标准的扩展,为用户提供丰富的物理验证方案 -

远程开关机,支持桌面和机架部署 -

VVAC编译器,支持DPI-C接口自动编译 - 支持虚拟处理器和外设模型、可综合模型、验证测试加速等应用场景

HPE Compiler为HuaPro P2E融合多种验证场景打造了坚实的技术基础,在实际测试中,可通过一键式流程缩短30%-50%的验证周期,从而大大降低开发成本,助力大规模系统级芯片设计效率提升。

发布会上,芯华章首席技术官傅勇表示,“面对系统级芯片开发挑战,芯华章以技术为本、以客户为导向,提出敏捷验证的解决方案,其核心是以低成本在各个芯片验证与测试环境中,进行自动化和智能化的快速迭代,并提早实现系统级验证,透过统一的数据库和高效的调试分析,达成验证与测试目标的高效收敛。”

秉承敏捷验证理念,芯华章HuaPro P2E打造从软件、硬件到调试的整体解决方案,无缝集成芯华章昭晓Fusion Debug调试器,并借助自研的统一数据库XEDB,让跨模式调试无缝衔接切换,满足从SoC到Chiplet的新一代复杂芯片设计需求,从整体上降低芯片开发的成本、风险和难度。

当今时代,芯片支撑了工业、通信、医疗、交通等几乎所有科技领域与应用场景,是数字经济的发展基石。作为产业最上游的EDA企业,芯华章致力于提供先进的数字前端EDA工具,以完整的数字验证全流程工具,为产业用户打造敏捷验证方案,加速芯片设计中的算法创新和架构创新,赋能系统级应用开发,为数字经济高质量发展强芯固基。

关于芯华章