8月12日消息,台积电、三星、英特尔等晶圆制造大厂都在积极布局背面供电网络技术(BSPDN),并将导入尖端的逻辑制程的开发蓝图。据韩国媒体 The Elec 报道,继英特尔公布了其命名为“PowerVia”的背面供电技术将导入Intel 20A制程工艺之后,三星电子在此前日本VLSI研讨会上也公布了其背面供电技术的研究结果,也将用于其2nm制程工艺。

过去多年来,芯片都是像披萨一样由下而上,层层制造的。芯片制造从最小的元件——晶体管开始,然后还需要建立越来越小的线路层,用于连接晶体管与金属层,这些线路被称为信号互连线,当中还包括给晶体管供电的电源线。当芯片的裸片制造完成后,还需要把它翻转并封装起来。封装主要是对裸片进行保护,并提供了与外部的接口,使其真正成为一个商用化的芯片。

然而,随着晶体管越来越小,密度越来越高,互连线和电源线共存的线路层变成了一个越来越混乱的网络,堆栈层数也越来越多,可能需要穿过10 到 20 层堆栈才能为下方的晶体管提供供电和数据信号。

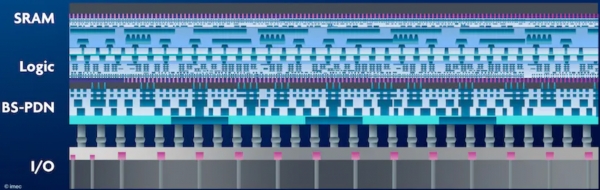

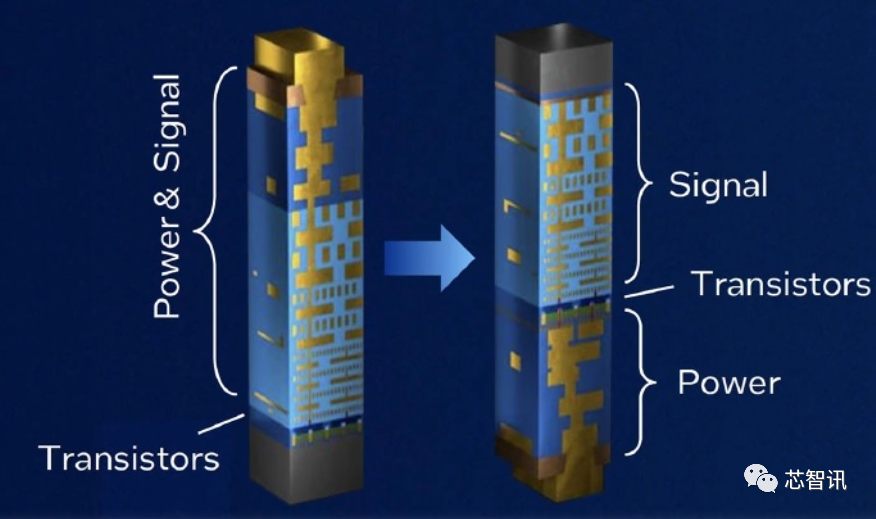

对此,领先的芯片制造商都在努力研究背面供电技术,即寻找将电源线迁移到芯片背面的方法,进一步使得芯片正面只需要专注于与晶体管的信号互连。也就是说,晶圆的制造将会先制造正面的晶体管,然后添加互联层,然后将晶圆反转,并对背面进行打磨减薄,在通过纳米硅穿孔(TSV)技术在晶圆背面进行制造供电网络,并与埋入式的电源轨连接。

在2023年VLSI研讨会上,英特尔就展示了制造和测试其背面供电解决方案PowerVia的过程,并公布已经有良好性能的测试结果。据英特尔介绍,电源线原本可能占据芯片上面20%的空间,但是其PowerVia背面供电技术,使得这些原本在上面的电源线不再需要,这也意味着互连层可以变得更宽松一些。

根据英特尔的Blue Sky Creek的测试芯片(该芯片采用英特尔即将推出的PC处理器Meteor Lake中的P-Core性能核心),证明了PowerVia解决了旧的“披萨式”制造方法所造成的问题,即电源线和互连线可以分离开来,并做得线径更大,以同时改善供电和信号传输。测试结果显示,芯片大部分区域的标准单元利用率都超过90%,同时单元密度也大幅增加,并有望降低成本。测试还显示,PowerVia将平台电压(platform voltage)降低了30%,并实现了6%的频率增益(frequency benefit)。PowerVia测试芯片也展示了良好的散热特性,符合逻辑微缩预期将实现的更高功率密度。

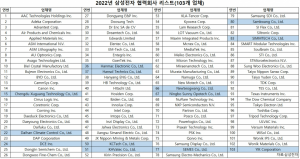

而根据最新的报道显示,在今年6月底的日本 VLSI 研讨会上,三星电子发表的一篇论文称,与传统的前端 PDN (前端供电网络)相比,其所研发的背面供电网络技术的应用,使其未公开的处理器面积缩小了14.8%。同时,该论文还特别强调了两个基于Arm架构的处理器,在采用了BSPDN技术之后,他们观察到的芯片面积分别减少了10.6% 和 19%,这也意味着成本和功耗的降低。同时也意味着,如果芯片面积保持不变的情况下,芯片内部的晶体管数量可以增加10% 到19%,性能也有望提升10%到19%。

▲ 三星BSPDN 研究成果(来源:三星)

三星在其论文中还提到,其背面供电 技术的另一大优势在于,使得布线长度减少了9.2%。背面供电技术通常支持更粗的电线和更低的电阻,因此可以驱动更高的电流以获得更高的性能或降低功耗,布线长度的进一步减少也将带来额外的性能优势。

另有市场消息称,台积电将会在 2025 年量产2nm(N2)制程,并计划 2026 年推出 N2P 制程,这个制程也将会采用背面供电技术。

编辑:芯智讯-浪客剑