半导体制程技术逼近已知的物理极限,为了持续强化处理器性能,小芯片(Chiplet)、异质整合技术乃蔚为潮流,更被视为延续摩尔定律的主要解决方案,世界大厂如台积电、intel、三星等,都在全力开发相关技术。

SiP、Chiplet 是什么?

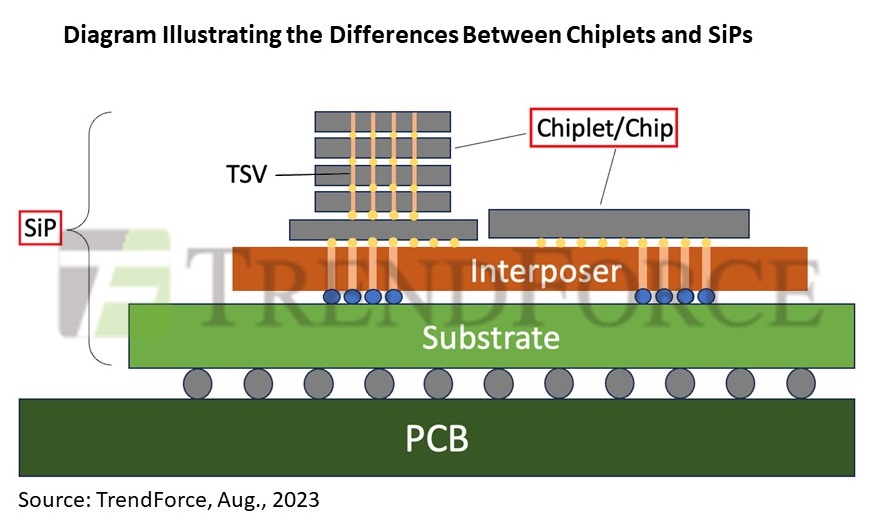

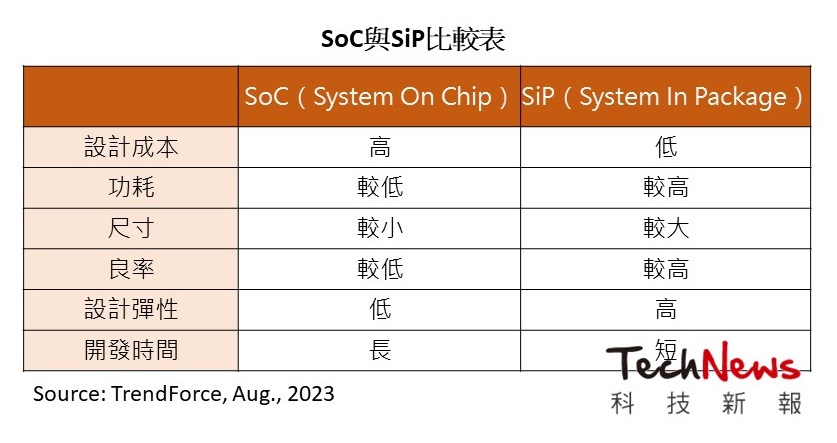

要了解 Chiplet 技术,需先理清目前常见的两个名词,分别是 SoC 与 SiP。SoC(System on Chip)是将数个不同芯片,经过重新设计使其全部使用“同样制程工艺”,并整合于单一芯片上;而 SiP(System in Package),是将数个“不同制程工艺”的芯片,通过异质整合技术对其进行连接,并整合于同一个封装壳内。

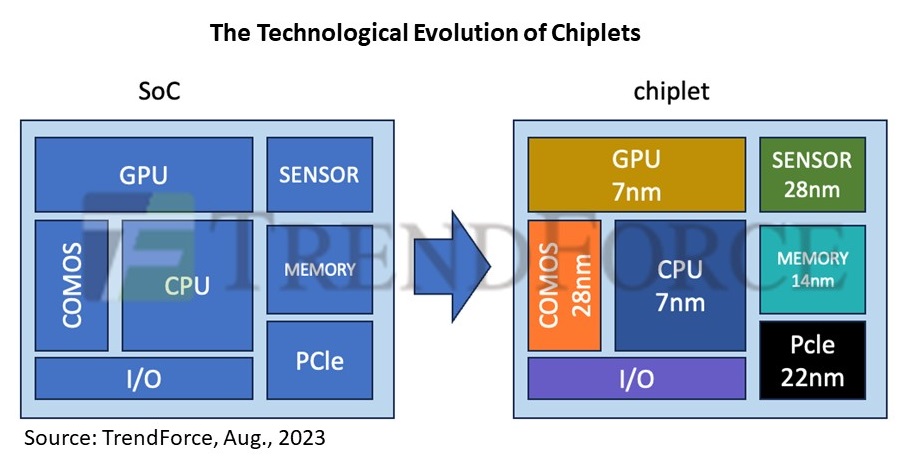

而 Chiplet 技术便是通过先进封装技术让多个小芯片形成的 SiP,它能够将具备不同功能的小芯片,通过先进封装技术整合于单一基板上。Chiplet 与 SiP 看似相同,但 Chiplet 本质还是芯片,而 SiP 是封装型态,两者在功能和用途上存在差异。

▲Chiplet 与 SiP 差异图

Chiplet 成为当今半导体发展趋势

Chiplet 技术的 SiP 设计概念,对比 SoC 呈现出多种优势,Chiplet 可以大幅提高芯片制造的良率。近年来,为力求芯片性能提高,芯片面积持续放大。芯片良率则随着芯片面积放大而下降。毕竟一个微小缺陷便足以使一颗大芯片报废,而 Chiplet 技术则可以整合面积相对小、制造良率相对高的各种小芯片来提升芯片性能及其制造良率。

其次,Chiplet 技术亦有利于降低设计的複杂度和设计成本。Chiplet 可以通过异质整合将各类小芯片整合在一起,不仅降低初期设计阶段的整合压力,也让设计和测试阶段更容易进行。此外,由于不同的小芯片可以独立优化,最终的整合产品往往能够获得更好的整体性能。

Chiplet 有望降低晶圆制造的成本。在芯片中,除了 CPU、GPU 以外,其他单元不依赖先进制程也能够发挥很好的性能。Chiplet 能让不同功能小芯片使用其最适合的制程,更有助于降低制造成本。

随着半导体制程的演进,芯片设计难度更高、流程更加複杂,设计成本亦持续攀升。在此趋势下,能够简化设计、制造流程且有效提升芯片性能、延续摩尔定律的 Chiplet 技术也被业界寄予厚望。

▲Chiplet 技术演进

Chiplet 应用发展

近年全球半导体大厂如 AMD、台积电、英特尔、英伟达等皆嗅到此领域的市场机遇,纷纷加紧布局 Chiplet 技术。例如AMD近年产品多受益于“SiP + Chiplet”的制造模式;另外,苹果发佈的 M1 Ultra 晶圆也通过定制的 UltraFusion 封装架构实现了极高的性能。在学术界,美国加州大学、乔治亚理工大学以及欧洲的研究机构近年也逐渐开始针对 Chiplet 技术牵涉的互连接口、封装与应用等问题开始展开研究。

综上所述,由于Chiplet技术能有效降低设计成本、缩短研发工时、提高设计弹性与良率,同时拓展芯片功能,其必然成为高阶芯片持续发展过程中不可或缺的解决方案。

来源:technews