11月15日消息,随着半导体制程微缩越来越逼近物理极限,成本也越来越高昂,越来越多的厂商开始转向采用Chiplet的方式,将多个小芯片通过先进封装技术整合在一起,形成类似SoC的效果,以提升整体性能,并降低成本。

特别是在ChatGPT等生成式AI应用的带动下,市场迫切需要能快速处理大量数据的AI芯片,对于先进封装技术的需求因此也得到了进一步爆发。调研机构Yole Intelligence数据显示,全球先进芯片封装市场从2022年443亿美元成长到2027年660亿美元。其中,3D封装预计将占约25%(即150亿美元市场规模)。

在此背景之下,能够提升半导体性能的先进封装技术也成为全新的兵家必争之地。对此,台积电、三星和英特尔等制造大厂展开了激烈的竞争。目前,率先推出3Dfabric先进封装平台的台积电取得绝对领先的地位。为了迎头赶上,三星计划明年推出“SAINT”(Samsung Advanced Interconnection Technology,三星先进互连技术)先进3D芯片封装技术,能以更小尺寸的封装,将AI芯片等高性能芯片、存储芯片和处理器整合。

三星2021年推出2.5D封装技术“H-Cube”后,便一直加速芯片封装技术的开发。今年4月,三星表示提供封装统包服务(package turnkey service),处理从芯片生产到封测整个过程。

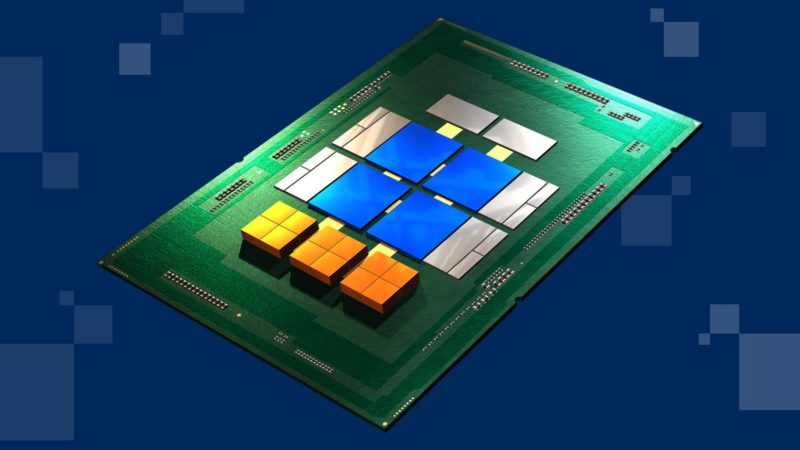

知情人士11月12日表示,三星计划在明年推出全新的“SANIT”品牌的3D先进封装技术:垂直堆叠SRAM和CPU的“SAINT S”;CPU、GPU等处理器和DRAM內存垂直封装的“SAINT D”、应用处理器(AP)堆叠的“SAINT L”。

其中,“SAINT S”等新技术已通过验证测试。但消息人士指出,三星与客户完成进一步测试后明年推出商用服务,目标是通过SAINT新技术,提高数据中心AI芯片及内置AI功能手机应用处理器的性能。

另外,根据外媒引用知情人士的消息指出,三星内部正考虑将其先进的3D封装技术应用于Exynos系列移动处理器上,有助于进一步提高Exynos处理器的整体性能和生产效率,并降低成本,进一步增强其产品竞争力。

除了三星之外,台积电也正在努力扩大其2.5D先进封装技术的(CoWos)的产能,并斥巨资测试和升级其3D芯片间堆叠技术“SoIC”,以满足苹果和英伟达等客户需求。台积电7月表示,投资新台币900亿元(约29亿美元)新建先进封装厂。

至于英特尔,其已经开始使用自家新一代3D芯片封装技术“Foveros”制造先进芯片。另外英特尔最新先进的对外开放的封装服务也将在2026年进入量产。不同于其他家主要提供以硅制程的中介层技术,英特尔计划采用更为先进的玻璃材质基板来替代传统基板,旨在助力英特尔实现在2030年前将单一封装芯片中的晶体管数量上限提高至1万亿个的目标。

11月初,世界第三大晶圆代工厂联华电子(UMC)也推出了晶圆对晶圆(Wafer-to-Wafer,W2W)3D IC项目,利用硅堆叠技术提供高效整合內存和处理器的尖端解决方案。

联华电子表示,W2W 3D IC项目雄心勃勃与日月光、华邦、智原科技(Faraday)和益华电脑(Cadence Design Systems)等先进封装厂及服务公司合作,以便充分利用3D芯片整合技术满足边缘AI应用的特定需求。

编辑:芯智讯-浪客剑