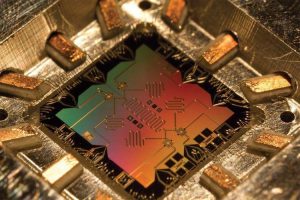

12月5日消息,当地时间周一,IBM公布了全新的量子计算芯片路线图,其中包括了名为“秃鹰(Condor)”的量子处理器,这是迄今发布的最大的基于Transmon的量子处理器,拥有1121个超导量子比特。

同时,IBM还推出了基于三个“鹭(Heron)”芯片的组合,每个芯片都有133个量子比特。像Heron和它的继任者“火烈鸟(Flamingo)”这样的较小芯片将在IBM的量子路线图中发挥关键作用 —— 该路线图也得到了重大更新。

基于这一更新,IBM将在2030年代末实现纠错量子位的工作,这是通过对Flamingo芯片的几次迭代中对单个量子位的改进而实现的。虽然,这些系统可能不会将现有的加密方案置于危险之中,但它们应该能够可靠地执行比我们今天所能做的任何事情都复杂得多的量子算法。

IBM 高级副总裁兼 IBM 研究院院长达里奥·吉尔 (Darío Gil) 表示:“我们正在进入一个时代,量子计算机将被用作探索科学新领域的工具。IBM 不断发展量子系统如何通过模块化架构扩展和提供价值。通过这样做,我们希望进一步提高实用程序的质量-扩展量子技术堆栈,并将其带到正在突破更复杂问题极限的用户和合作伙伴手中。”

IBM公司宣布的一切,包括现有的处理器,未来的路线图,未来几年机器的用途,以及使这一切成为可能的软件。但要了解该公司在做什么,我们必须回顾一下整个领域的发展。

量子位和逻辑量子位

使用量子位的几乎每个方面都容易出错。设置其初始状态、维护该状态、执行操作以及读出状态都可能引入错误,从而使量子算法无法产生有用的结果。因此,每个生产量子硬件的公司的主要关注点都是限制这些错误,并且在这方面取得了很大进展。

有迹象表明,这些进步现在已经让我们有可能在现有硬件上执行一些更简单的量子算法。这种潜力很可能会扩展到进一步的算法中,这要归功于我们在未来几年可能会看到的改进。

然而,从长远来看,我们不太可能让量子比特硬件达到错误率足够低的地步,以至于处理器可以成功完成可能需要在数小时计算中进行数十亿次运算的复杂算法。为此,人们普遍认为,我们需要纠错的量子比特。这涉及到将一个量子比特 —— 称为“逻辑量子比特” —— 持有的量子信息分散到多个硬件量子比特。附加的量子比特被用来监视逻辑量子比特的错误并允许它们的纠正。

使用逻辑量子位进行计算需要两个条件。一个是单个硬件量子位的错误率必须足够低,以便在新错误发生之前识别和纠正单个错误。(有迹象表明,硬件足够好,可以以部分效率工作。)你需要的第二件事是大量的硬件量子位,因为每个逻辑量子位需要多个硬件量子位才能工作。一些人估计,我们需要一百万个硬件量子位来制造一台能够承载大量逻辑量子位的机器。

IBM现在表示,预计到本十年结束时,它将拥有有用数量的逻辑量子位,IBM 院士兼IBM Quantum的副总裁杰伊·甘贝塔(Jay Gambetta)解释了昨天的公告如何符合这一路线图。

量子位和门

甘贝塔表示,该公司一直在采取双管齐下的方式来准备硬件。其中一个方面是开发持续制造大量高质量量子比特的能力。他说,1000 量子比特的Condor表明,该公司在这方面处于良好状态。甘贝塔说:“它的量子位大约小了50%,收益率就在那里 —— 我们的收益率接近100%。”

IBM一直致力于的第二个方面是限制在单个或对量子比特进行操作时发生的错误。这些操作称为门,它们本身可能容易出错。改变量子比特的状态会产生微妙的信号,这些信号会渗入邻近的量子比特,这种现象被称为串扰。Heron是新处理器中较小的一款,代表了四年来提高栅极性能的努力。甘贝塔说:“这是一个漂亮的设备,它比以前的设备好五倍,误差要小得多,而且串扰无法真正测量。”

许多改进都归结为在量子比特上引入了可调谐耦合器,这是该公司以前使用的固定频率硬件的一种改变。这加快了所有门的运行速度,有些门的运行速度提高了10倍。你花在量子位上的时间越少,出现错误的机会就越少。

该公司于2021年首次推出Eagle芯片,其中许多改进都在该芯片的多次迭代中进行了测试。该公司的新路线图将看到明年发布的133量子位Heron的改进版本,将实现5000个门操作。接下来将是明年的156量子位Flamingo处理器的多次迭代,到2028年,该处理器的门运算次数将达到1.5万次。

这些芯片还将连接在一起,形成更大的处理器,如Crossbill和Kookaburra,这些处理器也出现在IBM的路线图上(例如,七个火烈鸟可以连接在一起,形成一个与当前秃鹰具有相似量子比特数的处理器)。这里的重点将是测试在芯片内部和芯片之间连接量子位的不同方式。

使用它们

甘贝塔说,稳步提高的错误率将有助于人们利用现有的量子硬件完成实际工作。他强调了IBM今年早些时候发表的关于误差缓解的论文,该论文表明,对计算过程中发生的错误的详细了解,可以用来从现有硬件中挤出有用的结果。甘贝塔说,自从那篇论文发表以来,大约有六篇论文在arxiv上使用了类似的方法。但更重要的是,我们将展示(我认为现在的数字大约是13个)我们的用户、客户和合作伙伴的演示,他们有自己的使用量子计算机作为工具的演示。

虽然,这种方法在某些问题(包括模拟通用量子系统)上比经典计算的扩展性更好,但它最终会遇到硬件的限制 —— 甘贝塔提出的问题需要大约100个量子位和10000个门。超出这个范围需要纠错的逻辑量子位。

但如上所述,这些现在首次出现在路线图上。他们是循序渐进地这样做的。逻辑存储量子比特将在2026年展示,然后在第二年展示量子比特之间的逻辑通信。逻辑门将在2028年与Starling处理器一起出现,IBM预计将在2029年为Starling的迭代提供完整的软件包。这将使门操作大幅增加,从2028年火烈鸟的15000个门增加到2029年Starling的1亿个门。

但Starling可能远远达不到制造一个有用处理器所需的数百万个硬件量子位。甘贝塔表示,该公司将专注于减少托管一个强大的逻辑量子位所需的硬件量子位的数量,他指出,该公司今年早些时候在arXiv上发布了一份手稿,讨论了一种实现纠错的替代方案。目前最常用的测试方法(称为“表面代码”)可能需要多达4000个硬件量子位来承载12个逻辑量子位;手稿中描述的方案仅使用288个硬件量子位就可以做到这一点。

挑战在于,这种方法需要量子比特之间的连接,这些量子比特可能在一个芯片上相距遥远,或者可能完全在单独的芯片上。迄今为止,Transmon芯片与最近邻居的连接有限,这是表面代码所需要的全部,尽管甘贝塔说IBM已经证明其封装技术能够支持更长的连接。无论如何,未来几代量子处理器的一个关键焦点将是实现这些更远距离的连接。不同类型的耦合器将在2024年和2025年出现在路线图上,如果IBM要实现其十年目标,它们的高保真度将是绝对必要的。

考虑到这些特性并不是IBM这次宣布的某个功能的进化,它们可能被列为路线图上风险最高的项目。

软件也很重要

甘贝塔说,即使这一切都取得了成功,在这个十年末发布的硬件对于破解当今加密所需的复杂算法来说仍然太小。所以,纠错将会迎来这样一个时期,我们的硬件可以进行计算,这在经典硬件上是不可能的,但不能做我们最终想要用它们做的所有事情。这意味着软件开发将是决定我们在未来几年能实现什么目标的关键。

在这方面,IBM帮助开发了一个名为“Qiskit”的开源量子SDK,它在程序员可能希望看到的结果与直接向控制量子计算机的硬件发出命令的需要之间建立了一层抽象。这次的公告包括Qiskit发布了1.0版本,这表明该API已经稳定下来,未来的工作将更多地集中在现有技术的基础上构建有用的库。

另外,该公司还修改了其生成式人工智能编码工具,使其能够生成在Qiskit上运行的代码。

甘贝塔表示:“生成式人工智能和量子计算都处于拐点,在 WatsonX 上使用可信的底层模型框架简化了构建量子算法以探索实用规模的方式。”这是扩大量子计算范围并使其成为现实的重要一步。作为科学探索工具提供给用户。”

在接下来的几年里,开发和测试软件将变得越来越重要,因为我们还不完全清楚,在嘈杂的系统上减少错误,或者在有限数量的纠错量子比特上,能做些什么有用的事情。虽然很高兴看到IBM在年底前实现了2023年的处理器目标,但更大的新闻可能是它的路线图。在我们报道这个领域的整个过程中,人们一直在谈论开发纠错并展示它的小型演示。这是我们第一次看到以有用的形式显示到达日期。

来源:https://arstechnica.com/science/2023/12/ibm-adds-error-correction-to-updated-quantum-computing-roadmap/

https://newsroom.ibm.com/2023-12-04-IBM-Debuts-Next-Generation-Quantum-Processor-IBM-Quantum-System-Two,-Extends-Roadmap-to-Advance-Era-of-Quantum-Utility