2017年9月19日,“领先无界,英特尔精尖制造日”活动在北京正式召开。这应该是近10年来,英特尔首次在中国进行制造工艺技术的介绍活动。此次会议规格也是相当的高,英特尔公司全球副总裁兼中国区总裁杨旭、英特尔公司执行副总裁兼制造 运营与销售集团总裁Stacy Smith、英特尔高级院士、技术与制造事业部制程架构与集成总监Mark T. Bohr、英特尔公司全球副总裁兼中国区总裁Zane A. Ball等众多英特尔高管均出席了本次活动。

会上英特尔首次公布了自家最新的10nm工艺技术细节,并深度解析了英特尔的“摩尔定律”,揭开了目前业内关于制程节点命名上的“猫腻”,对于“摩尔定律已死”、“摩尔定律要靠三星、台积电来推动了”等言论给予了正面回击。

英特尔10nm工艺正式发布:领先对手整整一代

在今年CES上,英特尔CEO科再奇就曾预告,英特尔将会在今年下半年推出新一代的10nm工艺。今天,英特尔的全新10nm工艺终于正式在北京发布,同时还展示了基于英特尔尔10nm工艺的晶圆。英特尔表示,其10nm工艺拥有世界上最密集的晶体管和最小的金属间距,同时实现了业内最高的晶体管密度,领先其他竞争对手的10nm整整一代。

Intel执行副总裁兼制造、运营与销售集团总裁StacySmith首次展示了10nm晶圆,其将被用来制造CannonLake芯片。

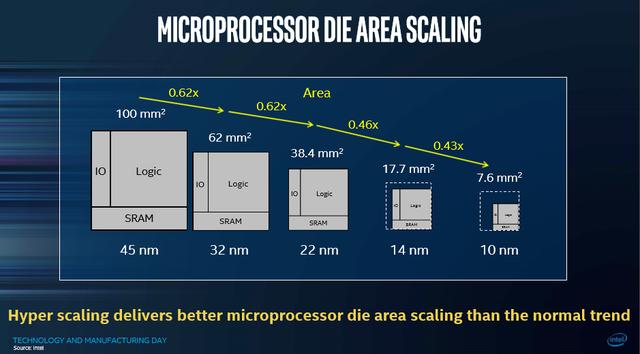

据介绍,英特尔10nm工艺采用第三代 FinFET(鳍式场效应晶体管)技术,加上超微缩技术 (hyper scaling),同时充分运用了多图案成形设计 (multi-patterning schemes),从而推出体积更小、成本更低的晶体管。

得益于10nm工艺的超微缩技术对于晶体管密度的提升,也使得芯片的die size缩小的幅度超过了以往。可以看到,22nm之前每代工艺的提升可带来die size约0.62倍的缩减,14nm以及10nm则带来了0.46倍和0.43倍的缩减。

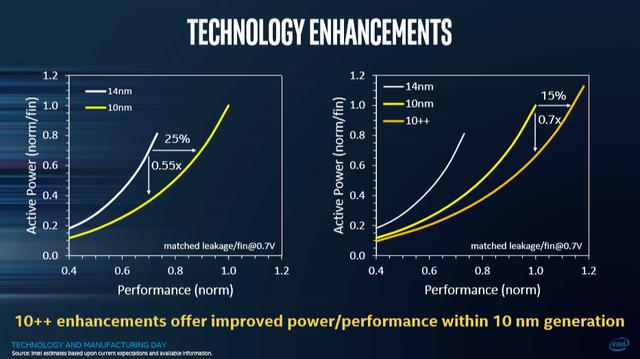

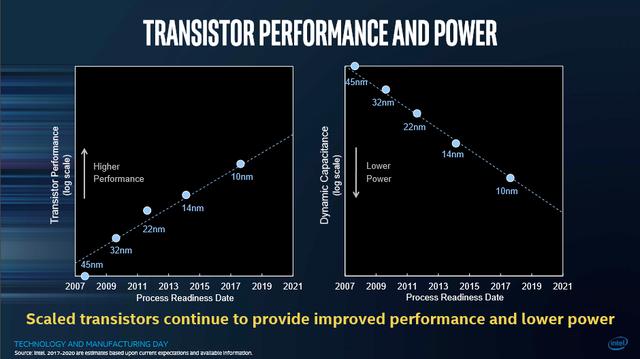

英特尔表示,相比之前的14nm制程,最新的10nm制程将可带来高达25%的性能提升和45%的功耗降低。此外,英特尔还将推出增强版的10nm制程——10 ,届时可将性能再提升15%或将功耗再降低30%。

英特尔10纳米制程将用于制造英特尔全系列产品,以满足客户端、服务器以及其它各类市场的需求。

摩尔定律依然有效,英特尔将推动摩尔定律继续前行

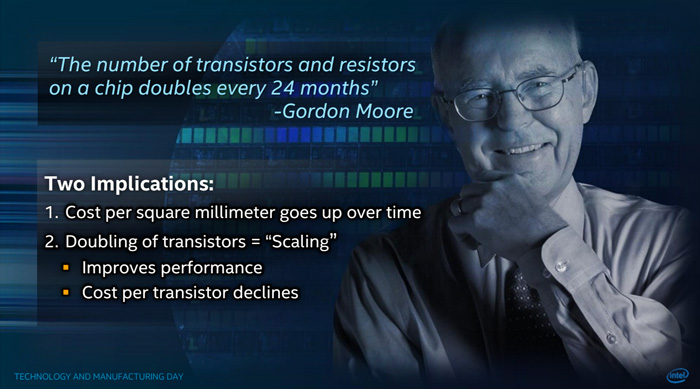

摩尔定律是由英特尔创始人之一的戈登·摩尔(Gordon Moore)于半个世纪前提出来的。其内容为,“当价格不变时,集成电路上可容纳的晶体管的数目,约每隔24个月便会增加一倍,性能也将提升一倍。也就是说,同样的成本下,每隔24个月,性能将提升一倍以上。这一定律揭示了半导体技术进步的速度。

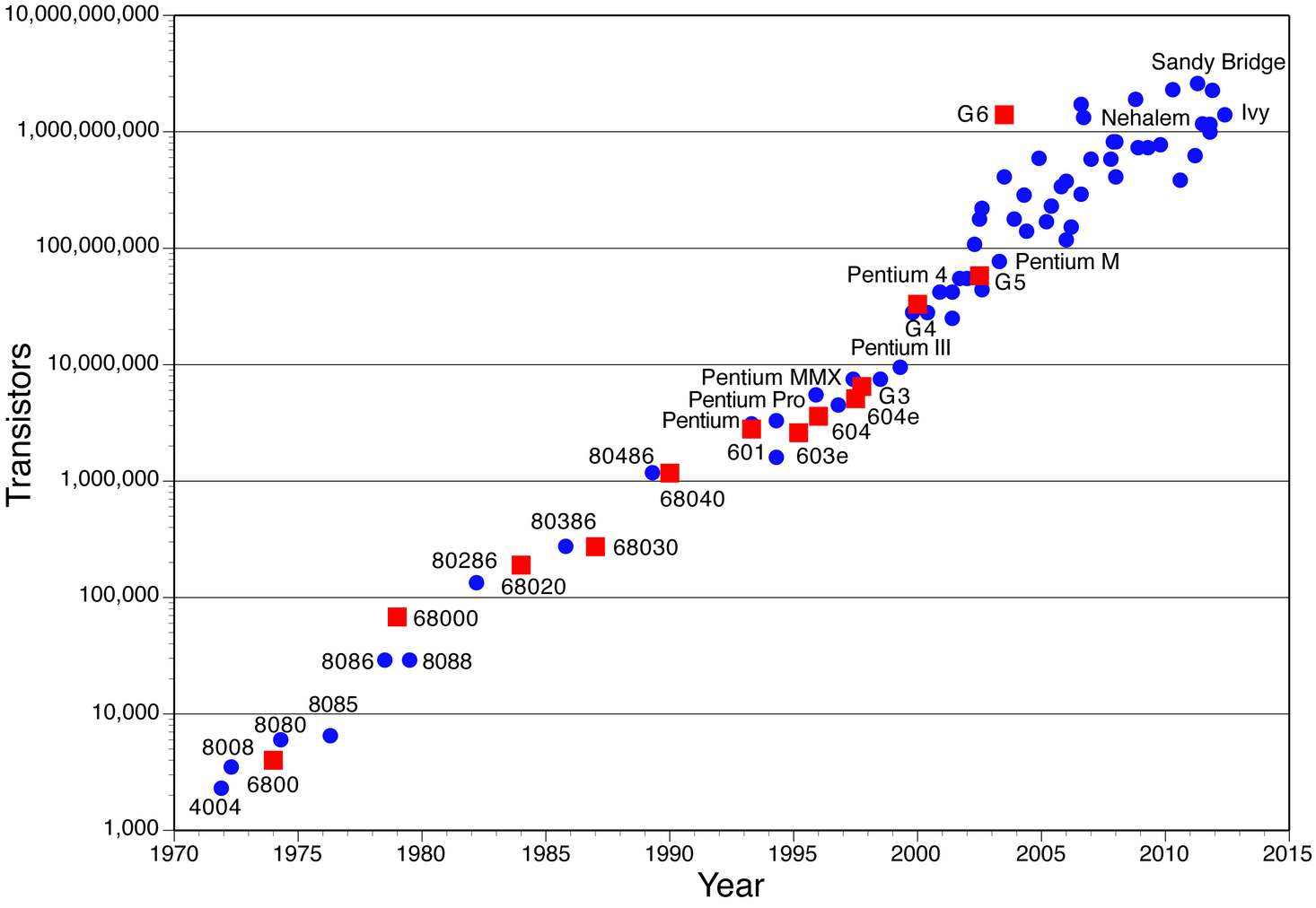

摩尔定律诞生之后几十年,半导体制程技术的发展也基本遵循着这一定律向前推进。反馈在芯片制程工艺命名上,也一直都是以前一代制程的0.7倍对新制程节点命名,因为这样的升级每一代的晶体管密度正好是上一代的两倍。所以,我们可以看到,英特尔90nm、65nm、45nm、32nm、22nm这样的命名,而且也基本是遵循每两年升级一代的规则。

但是自2011年下半年英特尔发布了22nm之后,近2年半之后,即2014年上半年,英特尔的14nm工艺才发布(二季度末才量产)。而在14nm向10nm提升的过程中,英特尔在工艺上遭遇了挑战,其Tick-Tock策略(即一年提升工艺,一年提升架构)甚至停摆。时隔3年之后的今天,英特尔才正式发布了新一代的10nm工艺。这也使得外界对于摩尔定律是否走已经失效产生了疑问,因为英特尔最近这两代的工艺都间隔了3年左右的时间,似乎打破了摩尔定律每两年升级一代的定律。

但是细心的网友应该发现,英特尔14nm与之前的22nm的命名并不是0.7倍之间的关系(22nm的0.7倍命名应该是16nm,14nm实际是22nm的0.64倍)。

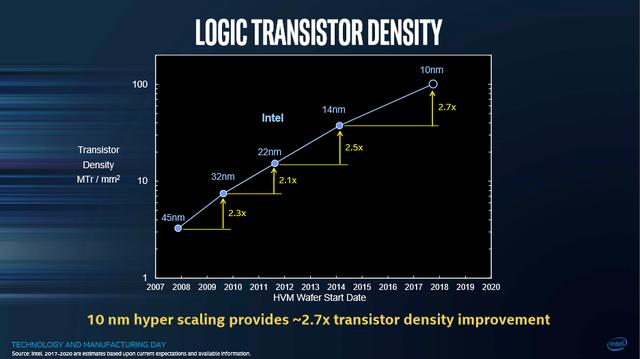

而且,根据英特尔的数据显示,从英特尔的32nm开始到后面的22nm,每两年的时间,晶体管密度(单位面积下晶体管的平均数量)的提升都超过了两倍(32nm的晶体管密度是45nm的2.27倍)。虽然英特尔从22nm升级到14nm,以及从14nm升级到10nm的时间周期都超过了两年,但是对应的晶体管密度也分别提升了2.5倍和2.7倍。

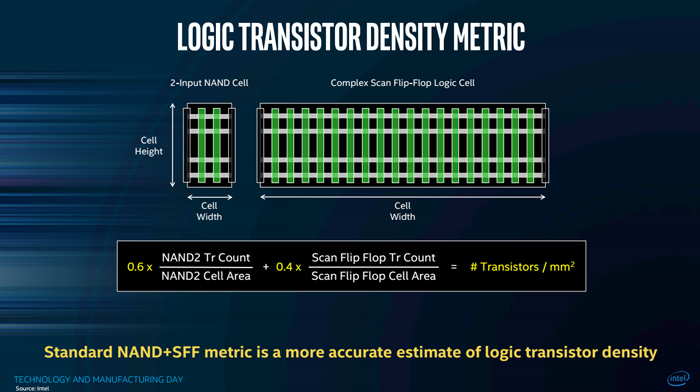

谈到晶体管密度,可能有些人不太清楚究竟如何来计算晶体管密度。

英特尔表示,一种简单的指标就是用栅极距(栅极宽度再加上晶体管栅极之间的间距)乘以最小金属距(互连线宽度加上线间距),但是这并不包含逻辑单元设计,而逻辑单元设计才会影响真正的晶体管密度。另一种指标——栅极距乘以逻辑单元高度——是纠正上述缺陷而朝着正确方向迈出的一步。但是这两种指标,都没有充分考虑到一些二阶设计规则。它们都不能真正衡量实际实现的晶体管密度,因为它们都没有试图说明设计库中不同类型的逻辑单元。此外,这些指标量化了比较上一代的相对密度,而真正需要的是给定面积(每平方毫米)内的晶体管绝对数量。在另一种极端条件下,用一个芯片的晶体管总数除以面积毫无意义,因为大量设计决策都会对它产生影响——例如缓存大小和性能目标等因素,都会导致这个值发生巨大变化。

其实在摩尔定律提出之时,对于晶体管密度就已经有了一个比较准确的计算公式。只不过这个公式并没有像摩尔定律一样被广泛的认知。这个计算公式基于标准逻辑单元的晶体管密度,并包含决定典型设计的权重因素。尽管任何设计库中都有各种标准单元,但是我们可以拿出一个普及的、非常简单的单元——2输入 NAND单元(4个晶体管),以及一个更为复杂、但也非常常见的单元:扫描触发器(SFF),结合对应的面积和权重比,最终得出晶体管的密度。

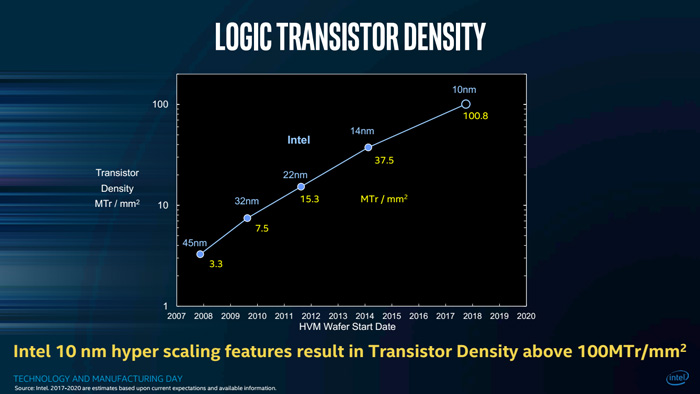

那么在这个计算公式之下,英特尔的各个工艺节点的密度又是多少呢?

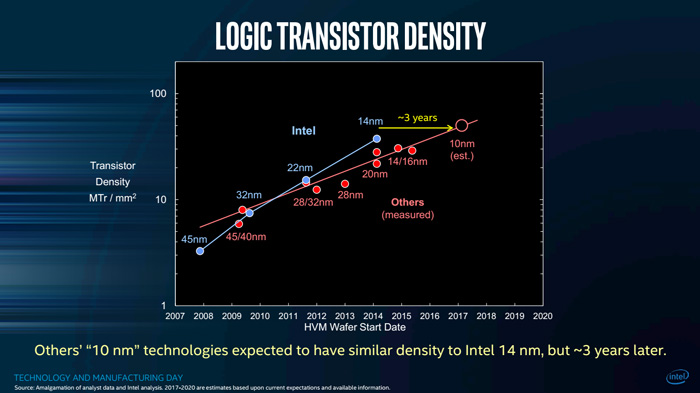

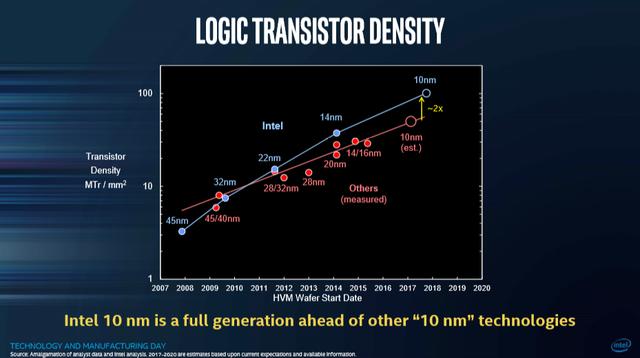

从上面这张图上我们可以看到,英特尔14nm工艺下的晶体管密度为37.5Mtr/mm²(百万晶体管/平方毫米),而这个密度是英特尔22nm工艺下晶体管密度的2.45倍。如果按照摩尔定律每两年翻一番的标准,两年半的周期,晶体管数量应该是需要增加2.5倍左右,所以英特尔的14nm工艺的晶体管密度也是基本符合摩尔定律要求的。

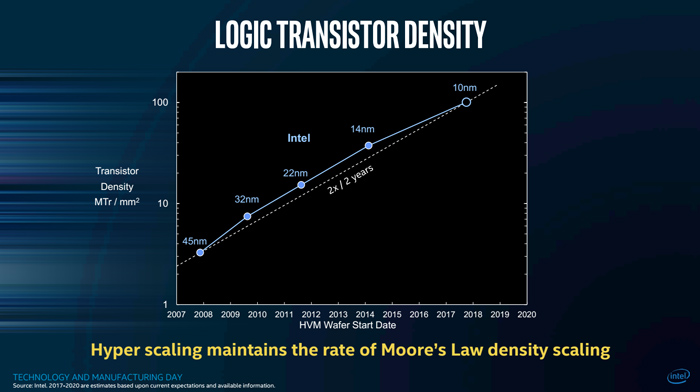

而此次英特尔发布的10nm工艺下的晶体管密度则达到了100.8Mtr/mm²,大约是上一代的14nm工艺的2.7倍,也就是说3年左右的时间内,英特尔实现了晶体管密度2.7倍的增长,虽然,略低于本该3倍的增长,但是结合此前几代超出摩尔定律的增长,英特尔10nm工艺仍然是符合摩尔定律的对于晶体管密度的线性增长要求(如下图)。

当然,摩尔定律除了要求每两年晶体管数量翻一番之外,还包括对于性能上的增长,成本上的下降的要求。

可以看到,英特尔每一代工艺的提升都带来了处理器性能的大幅提升和功耗的大幅下降。

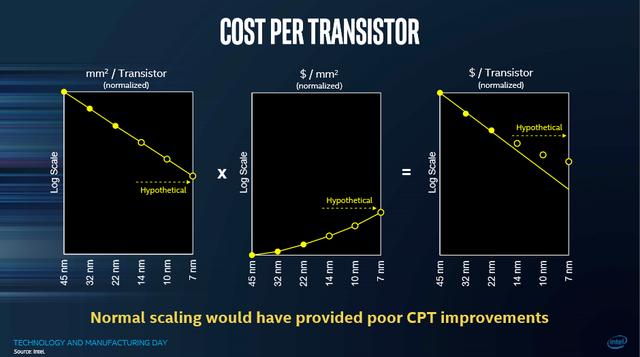

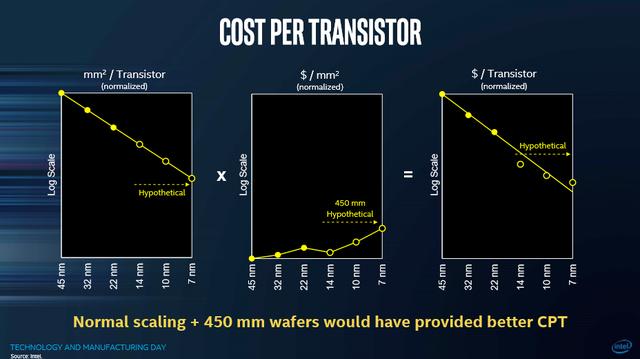

从成本方面来看,虽然芯片每平方毫米的成本是在不断上升的,但是随着晶体管密度的提升,同样数量的晶体管所占的芯片面积是在不断下降的,所以总体上来看,单位数量下的晶体管的成本不仅没有增长,而且是一直在下降的。根据英特尔的数据显示,其上一代的14nm和新发布的10nm工艺以及未来的7nm工艺都将带来晶体管成本的下降,虽然下降的幅度相比之前在放缓。

但是,如果结合450mm晶圆技术,则可以进一步减少单位面积下的晶圆成本,从而推动晶体管成本的加速下滑。

通过上面这一系列的数据,我们不难看出,在英特尔的推动下,摩尔定律依然有效,并正在继续向前推进。

“摩尔定律使计算得以普及。它是一个非常强大的经济学定律:按照特定节奏推动半导体制造能力的进步,我们就可以降低任何依赖于计算的商业模式的成本。”英特尔公司执行副总裁兼制造、运营与销售集团总裁Stacy Smith称:“想象一下,如果其它行业以摩尔定律的速度进行创新——性能每两年翻一番,那会发生什么?汽车能效:现在只需一加仑汽油,即可行驶相当于地球和太阳之间的距离;农业生产力:现在只用一平方公里土地,即可养活全部地球人;太空旅行:速度现在可以提升至300倍光速。这也是为什么摩尔定律如此重要的原因。”

英特尔高级院士、技术与制造事业部制程架构与集成总监Mark T. Bohr

英特尔高级院士、技术与制造事业部制程架构与集成总监Mark T. Bohr也表示:“逐一实现全新的制程节点变得愈加困难,成本也更加昂贵。仅仅是把设备安装到已有晶圆厂中,就要花费70亿美元。这也意味着半导体制造业将继续整合,因为越来越少的公司能承担得起推进摩尔定律的成本。英特尔每年都让产品价格更低、性能更强。推进摩尔定律的能力是我们的核心竞争力。我们确信,至少未来十年内,摩尔定律依然有效!”

此外,为了推动摩尔定律在未来的继续前进,以及可能的后摩尔时代的到来。英特尔还积极研究如纳米线晶体管、III-V 材料(如砷化镓和磷化铟)晶体管、硅晶片的3D堆叠、高密度内存、(EUV)光刻技术、自旋电子(一种超越CMOS的技术,当CMOS无法再进行微缩的时候,这是一种选择,可提供非常密集和低功耗的电路)、神经元计算等前沿项目。

友商制程节点命名上的“猫腻”

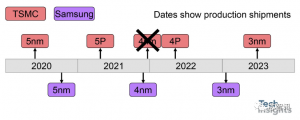

从英特尔的22nm之后,台积电、三星等半导体制程技术似乎也开始逐渐迎头赶上。虽然2014年英特尔就推出了14nm工艺,之后仅一年不到的时间,三星也推出了自家的14nm工艺,随后台积电也推出了其16nm工艺。2015年下半年发布的苹果iPhone 6s所搭载的A9处理器就分别采用了三星的14nm工艺和台积电的16nm工艺。去年年底,三星和台积电又相继推出了自己的10nm工艺,这也比英特尔的10nm工艺早了将近一年的时间。真的是三星、台积电的制程工艺开始赶超英特尔了吗?其实,这只是三星、台积电为了争夺市场,而采取的制程数字上的营销策略。

“随着摩尔定律的推进,制程升级也开始变得越来越难,一些公司开始背离了摩尔定律对于制程工艺的命名法则。即使晶体管密度增加很少,但他们仍继续推进采用新一代制程节点命名。这也导致了制程节点名称根本无法正确体现这个制程位于摩尔定律曲线的哪个位置。”英特尔高级院士、技术与制造事业部制程架构与集成总监Mark T. Bohr解释道。

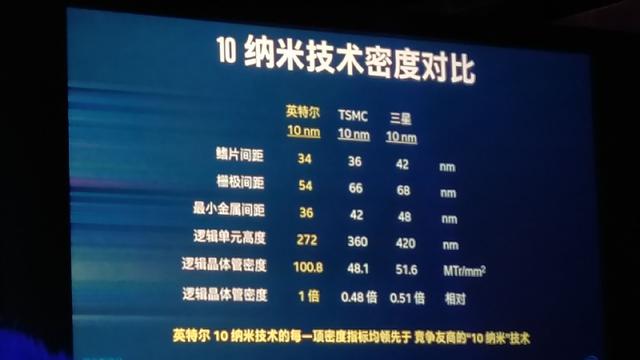

如果以前面提到的晶体管密度计算公式来作为标准的话,我们不难发现,英特尔三年前推出的14nm制程所能达到的晶体管密度已经与三年后台积电、三星所推出的10nm的晶体管密度相当。

英特尔最新的10nm制程工艺虽然比三星、台积电的10nm工艺推出时间略晚,但是它的晶体管密度却达到了后者的两倍。

此外,英特尔10nm的鳍片间距、栅极间距、最小金属间距、逻辑单元高度等指标均领先于台积电和三星的10nm。话说,英特尔的这个数据对比真的是让友商很受伤,可谓是“刀刀见血”。

在后续的专访环节,英特尔公司全球副总裁兼中国区总裁杨旭更是直言:“老虎不发威,当我们是病猫!”此外他还表示,“友商的下一代7nm也只相当于我们的10nm。”

我们都知道,以往英特尔在技术方面都比较低调,这次也是近10年来第一次在中国举办制程技术交流活动,相对于以往,英特尔在对于自家的制程技术宣传上变得更加高调,这样的变化背后,一方面可能是由于竞争对手的节点命名及营销策略让英特尔很不爽,另外一方面则是因为英特尔正计划大力开拓芯片代工业务。

去年8月,英特尔宣布开放代工业务,同时与ARM达成新的授权协议,英特尔将可以利用自己的制程技术代工ARM架构的芯片。今年,展讯发布的SC9861G-IA和SC9853,都采用了英特尔的14nm工艺代工。现在,英特尔还开放了22nm FFL以及最新的10nm制程,芯片代工市场又多了一个强大的玩家,台积电、三星想必是压力山大。明天我们将来详细介绍英特尔的代工业务的进展以及22nm FFL技术。

作者:芯智讯-浪客剑