在之前的文章,我们讨论了, 等大客户要求台积电增加多少CoWoS容量我们还解释了终端市场用例、CoWoS 容量分配以及 CoWoS 的需求方。

今天我们来谈谈供给侧。台积电正在向设备制造商紧急订购,填充其位于竹南的新先进封装。三星、英特尔、Amkor、JCET 和 ASE 也在扩展他们的竞争技术,以分得一杯羹。由于一些通用数据中心支出被生成型人工智能支出(例如内存和 CPU)所蚕食,了解仍在增长的支出对于了解供应链至关重要。

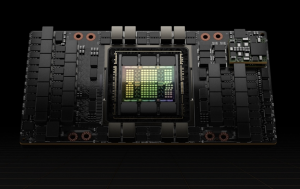

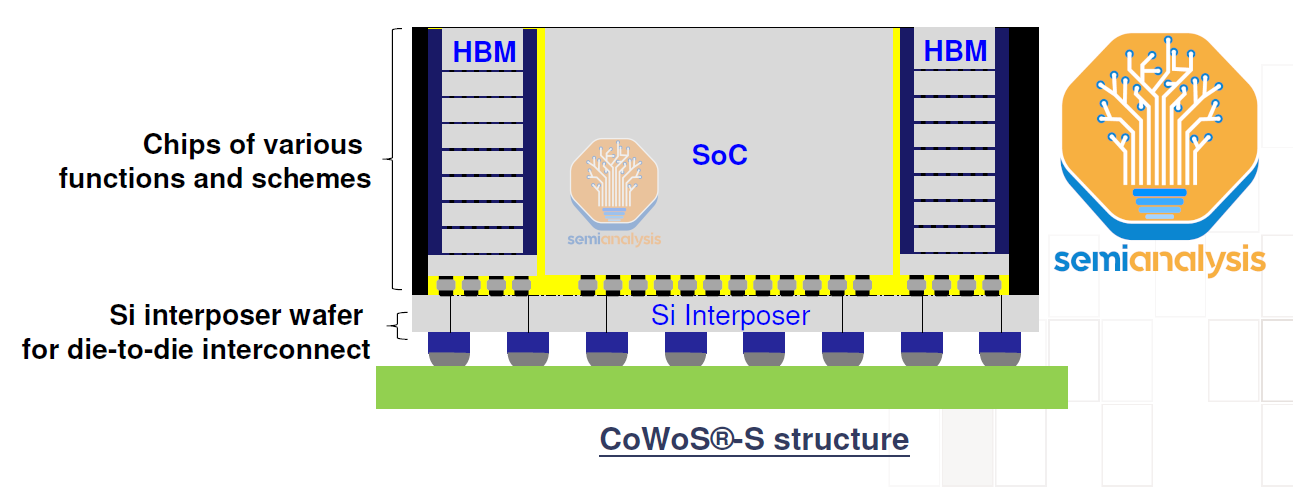

CoWoS 是台积电的一种“2.5D”封装技术,其中多个有源硅芯片(通常的配置是逻辑和 HBM 堆栈)集成在无源硅中介层上。中介层充当顶部有源芯片的通信层。然后将内插器和有源硅连接到包含要放置在系统 PCB 上的 I/O 的基板上。CoWoS 是最流行的 GPU 和 AI 加速器封装技术,因为它是共同封装 HBM 和逻辑以获得训练和推理工作负载最佳性能的主要方法。

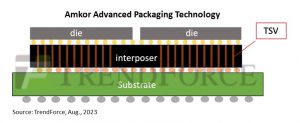

这就是为什么 2.5D 封装通常由领先的代工企业内部完成,因为他们可以生产硅中介层,同时还可以直接访问领先的硅。虽然日月光 (ASE) 和 Amkor 等其他 OSAT 已完成类似于 CoWoS 或 FOEB 等替代品的先进封装,但他们必须从 UMC 等代工厂采购硅中介层/桥接器。

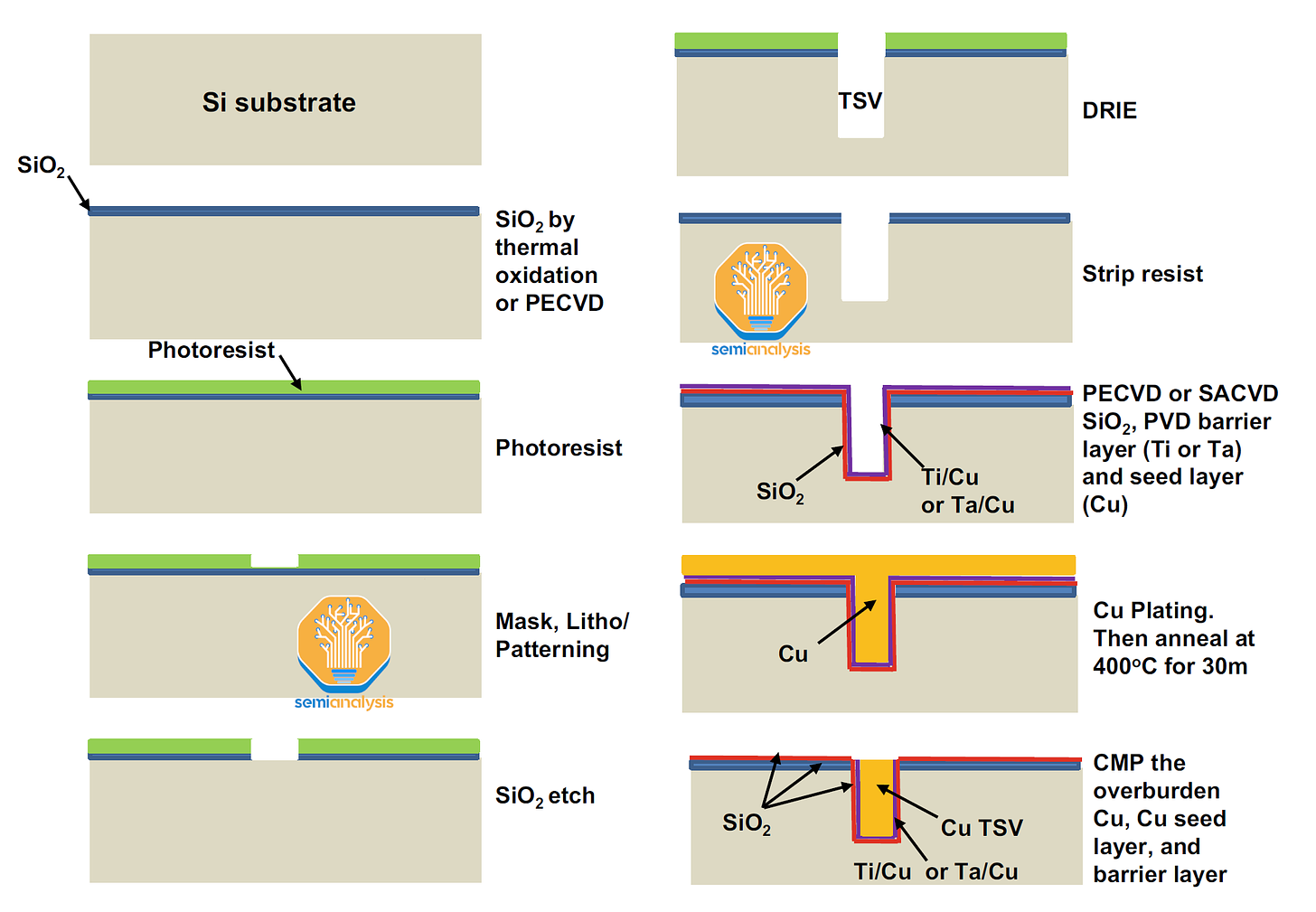

硅中介层的制造首先采用空白硅晶圆并生产硅通孔 (TSV)。这些 TSV 穿过晶圆,提供垂直电气连接,从而实现中介层顶部的有源硅(逻辑和 HBM)芯片与封装底部的 PCB 基板之间的通信。这些 TSV 是芯片向外界发送 I/O 以及接收电源的方式。

为了形成 TSV,晶圆上涂有光刻胶,然后使用光刻技术进行图案化。然后使用深反应离子蚀刻 (DRIE) 将 TSV 蚀刻到硅中,以实现高深宽比蚀刻。使用化学气相沉积 (CVD) 沉积绝缘层(SiOX、SiNx)和阻挡层(Ti 或 TA)。然后使用物理气相沉积 (PVD) 沉积铜种子层。然后使用电化学沉积 (ECD) 用铜填充沟槽以形成 TSV,通孔不穿过整个晶圆。

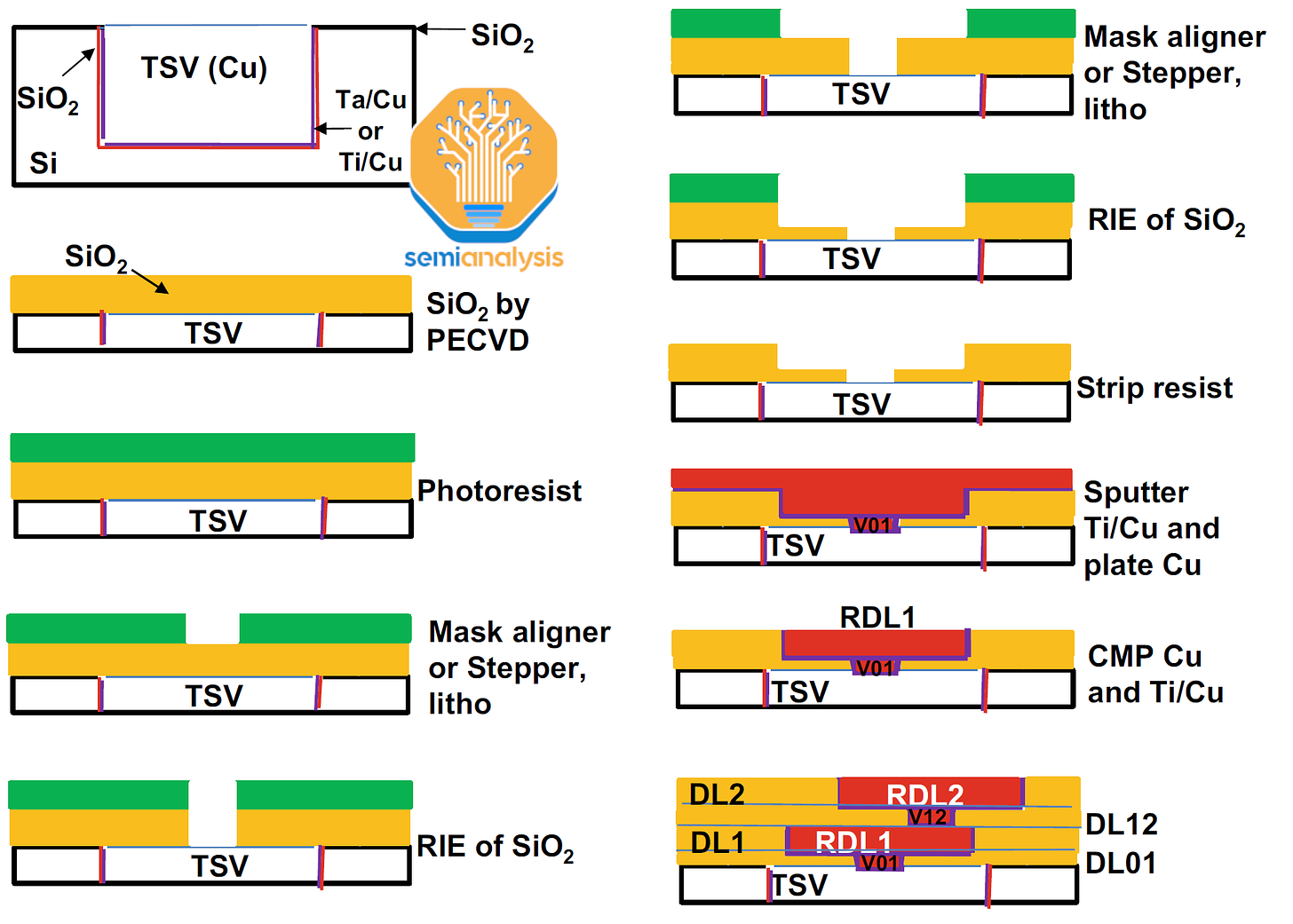

通过 PECVD 沉积二氧化硅 (SiO2),然后涂覆光刻胶并使用光刻对 RDL 进行图案化,然后使用反应离子蚀刻去除 RDL 通孔的二氧化硅。此过程重复多次,以在顶部形成较大的 RDL 层。

在典型的配方中,溅射钛和铜,并使用电化学沉积 (ECD) 沉积铜。然而,我们认为台积电使用极低 k 电介质(可能是 SiCOH)而不是 SiO2 来降低电容。然后使用 CMP 去除晶圆上多余的电镀金属。主要是标准的双镶嵌工艺。对于每个附加 RDL,重复这些步骤。

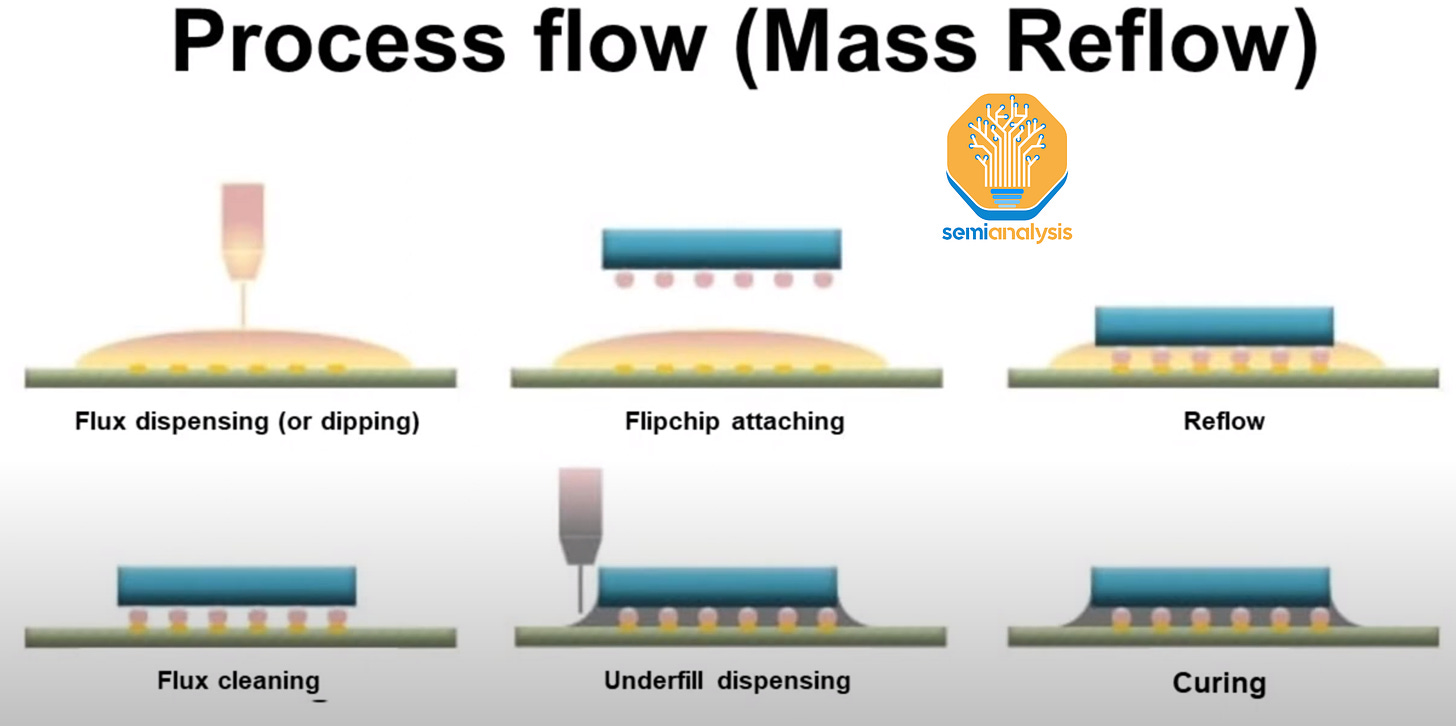

然后用树脂填充有源芯片和中介层之间的间隙,以保护微凸块免受机械应力。然后再次烘烤晶圆以固化底部填充胶。

尽管已变薄,但附接到中介层晶圆顶部的顶部管芯和封装可以为晶圆提供足够的结构支撑和稳定性,因此并不总是需要载体晶圆来支撑。

在下面 Nvidia A100 的 SEM 横截面中,我们可以看到 CoWoS 封装的所有各个元素。

请注意,A100 的中介层正面仅有单面 RDL。A100的架构更简单,只有内存和GPU,因此路由要求更简单。MI300由内存、CPU 和 GPU 组成,全部位于 AID 之上,因此这需要更复杂的 CoWoS 路由,从而影响成本和良率。

编译自:semianalysis