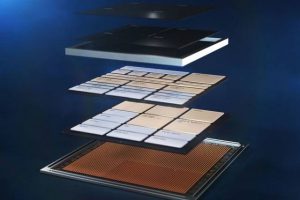

2024年1月12日消息,芯片设计服务大厂创意电子近日宣布,已成功于先进FinFET制程上实现复杂的3D堆叠芯片设计并完成投片,而该设计采Cadence Integrity 3D-IC平台,于复晶接合(flip-chip)封装的晶圆堆叠(WoW)结构上实现Memory-on-Logic三维芯片堆叠配置。

Cadence指出,Integrity 3D-IC平台中的Cadence Integrity System Planner与Cadence Innovus设计实现系统无缝整合,让复杂设计中的晶圆对晶圆界面规划和分层芯片堆叠得以实现。这款晶圆堆叠WoW设计已成功的通过首次硅片验证。

Cadence表示,针对WoW 3D堆叠应用,Integrity 3D-IC平台可提供芯片上(on-chip)以及芯片外(off-chip)的跨芯片的时序分析、电网规划、IR和热分析以及无缝接轨物理验证。为完成投片成功,创意电子采用特别为处理跨芯片3D规划和针对系统级分析的整合分析工具──Integrity 3D-IC平台。规划完成后,3D堆叠芯片在Innovus设计实现系统中全面实现设计,并以Voltus IC电源完整性解决方案执行IR分析,再透过Integrity 3D-IC平台进行系统级LVS验证。

创意电子设计服务资深副总经理林景源表示,在先进FinFET制程上让晶圆堆叠设计成功投片,激发真实的3D-IC技术未来潜质,我们又向前迈进一步。Cadence的Integrity 3D-IC平台能够在完整3D堆叠的所有层级上无缝工作,我们使用最先进的技术用于跨芯片的电路分割、时序分析、封装布局和分析等自动化技术在复晶接合封装上,实现复杂的堆叠芯片设计。Cadence 3D-IC平台解决方案的自动化和优异特性帮助我们处理高复杂、多芯片的堆叠设计,持续为先进FinFET制程上提供创新方案。

Cadence资深副总裁暨数字与签核事业群总经理滕晋庆表示,随着多芯片解决方案的研发,产业对其自动化的需求增加,我们更需要全面的解决方案,以因应堆叠芯片系统的芯片上以及芯片外的复杂度。Cadence的Integrity 3D-IC平台整合了3D-IC设计和分析功能,更结合了我们顶尖的SoC和封装设计实现技术与系统级规划和分

编辑:芯智讯-林子