5月20日消息,据韩国 ZDNet援引的最新行业消息称,韩国存储芯片大厂三星和 SK 海力士正计划使用1c制程的DRAM来开发下一代的HBM4内存。

据悉,三星最初计划在去年5月开始生产的HBM4中使用其1b DRAM(10纳米级第五代DRAM),而其现有的HBM3E产品则基于1a DRAM。但最新的消息显示,三星未能通过 英伟达最新 AI GPU(例如 Hopper 和 Blackwell)的资格测试,这也意味着三星仍无法获得英伟达的HBM3E订单,迫使三星考虑采用更先进的 1c DRAM 来打造新一代的HBM4。

爆料称,另一个关键原因是,三星认为1b DRAM其在功耗方面落后于竞争对手SK海力士。因此,三星计划将1c DRAM 用于 12-Hi(12层堆叠)HBM4和16-Hi(16层堆叠)HBM4 产品。三星预计将于2024年底建成第一条1c DRAM量产线,总产能约为每月3000片。最终的 HBM4 产品数据也不应该有太大差异。某些消息来源甚至强调,三星可能会在 2025 年中期提前开始量产,但这尚未得到证实。

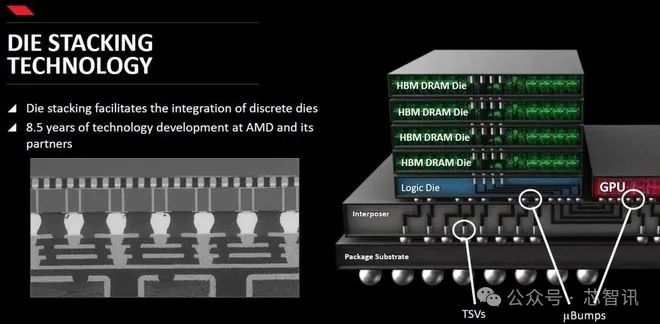

目前,三星和 SK 海力士都在竞相提供下一代 HBM4 内存标准,除了都选择1b DRAM制程之外,三星着眼于使用 3D 封装技术和多达 16-Hi 堆栈,以前所未有地增加 VRAM 容量和内存带宽。而SK 海力士则计划与台积电合作为其自己的 HBM4 解决方案采用新的封装技术。

在 2024 年台积电欧洲技术研讨会期间,台积电表示,由于 HBM4 内存从 1024 位接口转向 2048 位接口的复杂性,新的基础芯片将使用 N12 和 N5 工艺节点制造。

台积电设计与技术平台高级总监表示:“我们正在与主要 HBM 内存合作伙伴(美光、三星、SK 海力士)合作,在先进节点上实现 HBM4 全堆栈集成。” “N12 FFC+ 具有成本效益的基础芯片可以达到 HBM 的性能,而 N5 基础芯片可以在 HBM4 速度下以低得多的功耗提供更多逻辑性能。”

“我们与 Cadence、Synopsys 和 Ansys 等 EDA 合作伙伴合作,验证 HBM4 通道信号完整性、IR/EM 和热精度,”台积电代表解释道。

新的基础芯片将利用 CoWoS 技术(例如最近发布的 CoWoS-L 和 CoWoS-R 封装)来制造多达 16-Hi 堆栈的内存产品。除其他关键变化外,它还将利用新的通道信号完整性流程。拥有 5nm 节点将在功耗、性能和密度方面带来优势,因此可以期待明年发布用于下一代 GPU 加速器的下一代 HBM4 内存产品。

编辑:芯智讯-林子