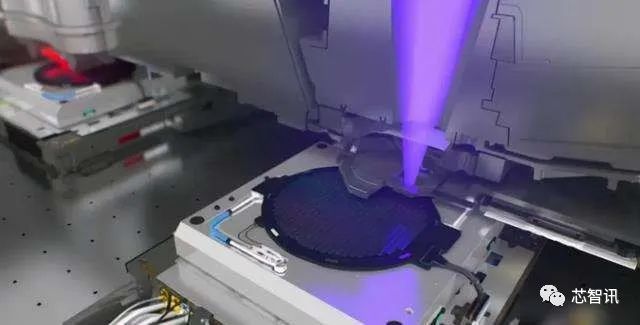

7月19日消息,据韩媒TheElec报道,与三星的3nm制程相比,明年即将量产三星2nm制程将会多出30%的极紫外(EUV)光刻层。

三星于2018 年首次开始在其 7nm 逻辑制程工艺节点上开始应用 EUV,从那时起,随着迁移到5nm,再到3nm,三星在芯片生产过程中的EUV光刻层的数量或EUV工艺步骤的数量也在持续增长。

报道援引消息人士的话表示,三星的2nm制程已经增加到了 20 层的EUV光刻层。而三星的1.4nm则预计将有30多个EUV光刻层。

与此同时,三星也将EUV应用于其DRAM生产。三星为其第 6 代 10nm DRAM 应用了多达 7 个 EUV 层,而 SK 海力士则应用了 5 个EUV光刻层。随着越来越多的芯片制造商扩大其EUV工艺步骤,光刻胶、空白掩模和薄膜等相关行业也有望增长。

根据三星此前公布的工艺路线图显示,2nm SF2制程2025年推出,较第二代3GAP 3nm制程,相同运计算频率和复杂度情况下课降低25%功耗,相同功耗和复杂度情况下课提高12%计算性能,减少5%芯片面积。

接下来的2nm SF2Z 制程采用了优化的背面供电网络 (BSPDN) 技术,该技术将电源轨置于晶圆背面,以消除电源线和信号线之间的瓶颈。与第一代 2nm 节点 SF2 相比,将 BSPDN 技术应用于 SF2Z 不仅可以提高功率、性能和面积 (PPA),还可以显著降低电压降 (IR 降),从而提高 HPC 设计的性能。SF2Z 预计将于 2027 年实现量产。

三星还公布了其他 2nm 工艺的发布日期。用于移动领域的 SF2 和 SF2P 将分别于 2025 年和 2026 年推出。针对人工智能和高性能计算的 2nm 工艺将于 2026 年推出,早于 BSPDN 工艺。该公司还将于 2027 年推出用于汽车的 SF2A 工艺。

编辑:芯智讯-浪客剑